an der Fakultät für Informatik

# LLVM Compiler Generator in OpenVADL

### **DIPLOMARBEIT**

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## **Software Engineering & Internet Computing**

eingereicht von

Kevin Per, Bsc.

Matrikelnummer 11731660

| der Technischen Universität Wien |                           |               |

|----------------------------------|---------------------------|---------------|

| Betreuung: Ao.Univ.Prof. DiplIng | . Dr.techn. Andreas Krall |               |

|                                  |                           |               |

|                                  |                           |               |

|                                  |                           |               |

|                                  |                           |               |

|                                  |                           |               |

| Wien, 27. November 2025          |                           |               |

|                                  | Kevin Per                 | Andreas Krall |

|                                  |                           |               |

# LLVM Compiler Generator in OpenVADL

## **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

## **Software Engineering & Internet Computing**

by

#### Kevin Per, Bsc.

Registration Number 11731660

| to the Faculty of Informatics     |                         |               |

|-----------------------------------|-------------------------|---------------|

| at the TU Wien                    |                         |               |

| Advisor: Ao.Univ.Prof. DiplIng. D | Or.techn. Andreas Krall |               |

|                                   |                         |               |

|                                   |                         |               |

|                                   |                         |               |

|                                   |                         |               |

|                                   |                         |               |

| Vienna, November 27, 2025         | Kevin Per               | Andreas Krall |

|                                   |                         |               |

|                                   |                         |               |

# Erklärung zur Verfassung der Arbeit

| 1/  | .:   | D- " | D    |

|-----|------|------|------|

| nev | וווי | Per. | DSC. |

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Ich erkläre weiters, dass ich mich generativer KI-Tools lediglich als Hilfsmittel bedient habe und in der vorliegenden Arbeit mein gestalterischer Einfluss überwiegt. Im Anhang "Übersicht verwendeter Hilfsmittel" habe ich alle generativen KI-Tools gelistet, die verwendet wurden, und angegeben, wo und wie sie verwendet wurden. Für Textpassagen, die ohne substantielle Änderungen übernommen wurden, habe ich jeweils die von mir formulierten Eingaben (Prompts) und die verwendete IT-Anwendung mit ihrem Produktnamen und Versionsnummer/Datum angegeben.

| Wien, 27. November 2025 |           |

|-------------------------|-----------|

| ,                       | Kevin Per |

# Acknowledgements

I wish to thank my parents and my sister, Grzegorz, Krystyna and Julia, for their mental and financial support throughout my academic journey.

I would also like to thank Prof. Andreas Krall for his support, guidance and excellent supervision during the course of this thesis.

Finally, I would like to thank the VADL team, especially Johannes and Benedikt, for their valuable feedback and collaboration.

# Kurzfassung

Das Entwickeln von Prozessoren ist eine arbeitsintensive Aufgabe. Jede Änderung erfordert Änderungen der Toolchain. Gleichzeitig benötigt schnelle Entwicklung auch schnelle Entwicklungsiterationen. Die Vienna Architecture Description Language (VADL) ist eine Prozessorbeschreibungssprache, wo die Spezifikation als goldenes Modell dient. Die quelloffene Implementierung, OpenVADL, generiert mehrere Artifakte für das schnelle Entwickeln von Prozessoren aus der Spezifikation. Diese Arbeit präsentiert den Compiler Generator für einen LLVM-basierten C Compiler.

Die größte Herausforderung ist die Ableitung von Instruktionsselektionsmustern aus den Instruktionsverhaltensgraphen in einer VADL Spezifikation. Unser Ansatz analysiert und klassifiziert jede Instruktion anhand des Instruktionsverhaltens, um dann systematisch Muster für jede Klasse zu generieren.

Schließlich werden die generierten gegen öffentlich verfügbare Compiler für die Architekturen RV32IM, RV64IM und AArch64 verglichen.

## Abstract

The development of processors is a labor-intensive task. Every design change requires the corresponding adaptation across the toolchain. At the same time, fast development requires fast iterations. The Vienna Architecture Description Language (VADL) is a processor description language in which the specification acts as golden model. Its open source implementation, OpenVADL, generates a variety of tools for rapid prototyping of processors. In this thesis, a compiler generator is presented that generates an LLVM-based C compiler from a VADL specification.

The biggest challenge is deriving the instruction selection patterns from the instruction behavior specified in the VADL specification. Our approach addresses this by analyzing and classifying instructions according to their behavior, and then systematically generating instruction selection patterns for each classification label.

Finally, we evaluated the generated compilers against the publicly available compilers for RV32IM, RV64IM and AArch64, respectively.

# Contents

xiii

| Κι | urzfassung                                                | ix            |

|----|-----------------------------------------------------------|---------------|

| Al | bstract                                                   | xi            |

| Co | ontents                                                   | xiii          |

| 1  | Introduction  1.1 Structure of this Work                  | <b>1</b><br>1 |

| 2  | Background                                                | 3             |

|    | 2.1 Compiler Backend                                      | 3             |

|    | 2.2 Processor Description Languages                       | 17            |

|    | 2.3 Vienna Architecture Description Language              | 19            |

|    | 2.4 OpenVADL                                              | 24            |

| 3  | Implementation                                            | 29            |

|    | 3.1 Research Questions                                    | 29            |

|    | 3.2 Overview                                              | 30            |

|    | 3.3 Encoding Generation                                   | 31            |

|    | 3.4 Predicate Generation                                  | 32            |

|    | 3.5 Operand Detection                                     | 33            |

|    | 3.6 Instruction Classification                            | 34            |

|    | 3.7 Lowering Machine Instructions                         | 37            |

|    | 3.8 Lowering Pseudo Instructions                          | 40            |

|    | 3.9 Lowering Registers                                    | 41            |

|    | 3.10 Relocations                                          | 42            |

|    | 3.11 Instruction Expansion                                | 43            |

|    | 3.12 Constant Materialization and Register Adjustment     | 43            |

|    | 3.13 Conditional Branch and Compare-and-Jump Instructions | 44            |

|    |                                                           |               |

| 4  | Problems                                                  | 45            |

|    | 4.1 Recursive Lowering                                    | 45            |

|    | 4.2 Frontend and Backend Type Mismatch                    | 46            |

|    | 4.3 Truncation                                            | 46            |

| 4.4          | Register index with different register files   |

|--------------|------------------------------------------------|

| 4.5          | 1 1                                            |

| 4.6          | Instruction Alignment                          |

| 4.7          | 7 Type Mismatches during Instruction Expansion |

| 4.8          | B Free Truncations and Extensions              |

| 4.9          | Application Binary Interface                   |

| 5 Ev         | valuation                                      |

| 5.1          | RISC-V                                         |

| 5.2          | 2 AArch64                                      |

| 6 R          | elated Work                                    |

| 6.1          | LISA                                           |

| 6.2          | 2 ArchC                                        |

| 6.6          | <u> </u>                                       |

| 6.4          | 4 Original VADL Compiler Generator             |

| 6.5          | 5 VEGA                                         |

| 6.6          | 6 Completeness and Translation Validation      |

| <del></del>  | iture Work                                     |

|              |                                                |

| $7.1 \\ 7.2$ | G I                                            |

| 7.3          | <u> </u>                                       |

| 1.6          | Constant Sequences                             |

| 8 C          | onclusion                                      |

| Over         | view of Generative AI Tools Used               |

| List (       | of Figures                                     |

|              |                                                |

| List         | of Tables                                      |

| List         | of Algorithms                                  |

| Acro         | nyms                                           |

|              | ography                                        |

CHAPTER 1

# Introduction

Moore's law predicted that the number of transistors on a chip would double every 18 months. While this has been true for many decades, modern engineering has struggled to keep up lately. New applications, such as artificial intelligence, have entered the stage and require new engineering paradigms to meet their power and performance demands. In recent years, computation has moved from homogeneous general-purpose processors to co-processors, that are tailored for specific applications. Artificial intelligence is now trained on hundreds of GPUs. While training of large language models is being done in large data centers, even consumer hardware added additional processors for acceleration. This heterogeneous paradigm, which offloads computation to additional processors, is not new but quite popular at the moment. General-purpose processors need a lot of power and chip area. However, as stated in GM04, p2], flexibility and energy efficiency are competing goals. The word "flexibility" is understood as using a single processor for multiple applications.

By introducing a new Processor Description Language (PDL), we would like to ease the design flow of prototyping a new processor Fre+. This thesis introduces a compiler generator to target an Application Specific Integrated Processor (ASIP). Given a specification in the Vienna Architecture Description Language (VADL), presented in Fre+, OpenVADL's compiler generator can generate a compiler.

#### 1.1 Structure of this Work

Chapter 2 provides essential context on the operation of compiler backends and VADL. Chapter 3 discusses implementation details. Chapter 4 addresses key limitations of the current implementation, while Chapter 7 considers future directions and shows possible extensions. Chapter 5 discusses the performance of the generated compiler. Chapter 6 presents related PDLs, which inspired VADL. Finally, Chapter 8 presents a conclusion, final reflections and tying together findings and their implications.

CHAPTER 2

# Background

This chapter describes the most important aspects of a compiler backend and introduces VADL.

### 2.1 Compiler Backend

A compiler is separated into multiple modules. While a modern compiler like LLVM has many components, there are three major modules: frontend, middleend and backend.

- The frontend handles the input language like for example C or C++. Programs are parsed, type checked and finally converted into an Intermediate Representation (IR) e.g. the LLVM Intermediate Representation (LLVM IR).

- The *middleend* applies *target-independent* transformations on the IR. These optimizations are independent of the programming language and the target-machine.

- The backend lowers the IR to assembly or machine code to produce an executable program for the hardware and applies optimizations based on the target Instruction Set Architecture (ISA), which defines the instructions supported by a processor.

Compiler backends can be distinguished into three essential phases: instruction selection, instruction scheduling, and register allocation. These three phases will be discussed in more detail in this chapter. The next section discusses different intermediate representations commonly used in compilers.

#### 2.1.1 Intermediate Representations

A textual representation of a program would be too difficult to optimize. Compiler frontends create an IR with properties more suitable for optimizations. There are many

different kinds of IRs. A classification overview is presented in [Coo12], p162]. A program traverses multiple representations during the compilation until it is transformed to assembly or machine code. In practice, a compiler has multiple representations of a program because different compilation stages require different levels of abstraction and analysis.

#### **Abstract Syntax Tree**

An Abstract Syntax Tree (AST) is a tree-structured representation of an input program. It is abstract because it omits irrelevant details, such as the code's formatting and comments. Therefore, it encapsulates a program's syntactic structure. A node represents a syntactic element and an edge is a structural relationship between two nodes. Internal nodes are statements or operations in the tree. While leaf nodes are variables or constants. The AST is usually the first IR in the compilation process.

#### Control Flow Graph

A Control Flow Graph (CFG) represents the order of execution as a graph. Each node represents a basic block. A directed edge in a CFG models the control transfer between different basic blocks. A basic block is a sequence of instructions where control flow can only enter at the beginning and can exit only at the end. The terminator is the last instruction of the block and determines which basic block is executed next. Common terminators are unconditional jumps, conditional jumps and return instructions. Some CFG representations can model a fall-through where no explicit terminator is required and the next successor is automatically executed next. A CFG represents all possible execution paths in a function [Coo12], p170].

#### Static Single Assignment Form

Static Single Assignment Form (SSA) is not an IR itself. It indicates that the IR's operations uphold certain guarantees [RB22]. In this representation, every variable has only one definition, and multiple definitions are joined by a phi function when control flow merges. A phi function is called a phi node when the IR is graph-based. A phi function's semantics is to copy the value depending on the edge from which the predecessor basic block originates. In practice, SSA has an unlimited number of *virtual registers*. Since only one definition is allowed, a virtual register represents a version of a variable. According to [Coo12], p194], this form has the benefit of simplifying lifetimes of values for optimizations.

#### **Dataflow Graph**

A Data Flow Graph (DFG) is a graph-based IR that depicts the data flow between nodes. A node represents an operation in a program, and a directed edge represents an operation's input. A drawback is that conditionals have to be modeled using select or phi nodes in a DFG as conditionals require exclusive execution, with only one branch active at a time. On the other hand, parallel execution executes both branches independently

WP94. A select node is an operation that chooses one of multiple input values based on a boolean condition.

#### Program Dependence Graph

Another graph-based IR is the Program Dependence Graph (PDG). It combines both a control-dependence and a data-dependence graph into one representation [Kuc+81] FOW87 Muc06, p284. Each node represents an operation in the program. The controldependence subgraph shows whether a node A can directly affect whether a node B is executed. A data-dependence is a constraint between two statements A and B where the reordering of the nodes would result in an incorrect result [Muc06, p268]. There are different kinds of data-dependence constraints. If A writes a value which B reads then the constraint is called flow dependence. If A reads a value which B writes then the constraint is called anti dependence. If A and B set the same value then the constraint is called *output dependence*. If both A and B read a value from some variable then the constraint is called *input dependence*. The data-dependence constraints modeled as directed edges between two statements are summarized in a data-dependence graph. The benefit of this IR is that the optimizing compiler can enable powerful optimization by inspecting the graph. The compiler can safely reorder instructions since the dataflow constraints are modeled in the graph. Additionally, the graph enables loop transformations like loop fusion or vectorization [FOW87].

#### Linear IRs

According to [Coo12], p175], "Linear IRs represent the program as an ordered series of operations". Cooper continues by defining that a one-address code models data through the stack or accumulator registers. A three-address code represents an operation with two source operands and a result. Three-address code is also called quadruple code because operation code, two source operands and a result are composed to a tuple of four components. A linear IR has two benefits. First, it is very close to a hardware representation since assembly code is also linear. Second, the IR is easily serializable and deserializable. This is an important property for debugging. On the other hand, linear IRs do not typically contain high-level constructs such as loops. This is a problem for advanced optimizations, since retaining metadata like the loop stride enables more effective optimization analyzes.

Typically, linear IRs are embedded in a CFG where each basic block has a linear sequence of instructions.

#### Hybrid IRs

Hybrid IRs are a mixture of multiple kinds. An example is Multi Level Intermediate Representation (MLIR) [Lat+21]. MLIR is structured into many different dialects. A dialect is an IR extension which defines a set of domain specific operations. Each dialect is also responsible for individual transformations and optimizations. Each dialect has its

own abstraction because some define high-level constructs, while others define low-level details. By progressively lowering the dialects, the IR becomes unified. Lowering is the process of transforming one dialect into another dialect. For most dialects the lowering ends with the LLVM dialect which can be translated to LLVM IR.

#### LLVM IR

The LLVM compiler frontend reads a source program and translates it into LLVM IR. The middleend applies target-independent optimizations, while the backend maps the IR into machine instructions. LLVM IR has two external representations: a bitcode and a human-readable textual format. The representation is composed of multiple modules, each serves as a compilation unit for the concurrent translation. LLVM IR is statically typed and is in SSA Anoi.

The type system supports primitive types, labels, aggregate types, and functions. LLVM IR has attributed that support optimizations. For example, arithmetical instructions can indicate whether overflow or underflow can occur. Similarly, functions can also carry attributes, for example, to disable inlining. Floating point instructions can set fast-math flags that enable aggressive optimizations that may modify the result Anoil. However, one problem with LLVM IR is that it is very low-level. Because there is no explicit construct for loops, it is harder to apply loop optimizations. Typically, a loop's backedge is modeled with an unconditional jump to the basic block, which acts as the loop header. To address this, LLVM's middleend includes passes to recalculate loop bounds that are lost during translation Anok Anok Listing 2.1 shows a simple function that has three arguments %a, %b and %c. %a, %b are integers and %c is a function pointer. The function has three basic blocks entry, if then and if end. The two arguments a and b are compared with a **xor** operation and the result is stored into the virtual register %0. Based on the value of \%0, the control flow continues with basic block if then or if end. If both arguments are equal then the function pointer in virtual register %c is called. Afterwards, an unconditional jump jumps to the block if.end which returns from the function. If both arguments are not equal then the control flow immediately continues with basic block *if.end* and returns from the function.

#### 2.1.2 Instruction Selection

In general, compilers translate source code into assembly or machine code, which is then executed by a target-machine. The process of mapping  $\overline{\text{IR}}$  operations to machine instructions is called instruction selection. It is important that the selected instructions are semantically equivalent to the original program. While there are many possibilities to express semantic equivalence, instruction selectors compute a selection with the minimal cost.

For example, some architectures support a fused-multiply-add instruction. The instruction selector can choose whether it is profitable to use the fused instruction or separate additions and multiplications. Instruction selection can significantly influence the program's performance and size.

```

1 define void @bool_eq(

i1 zeroext %a, i1 zeroext %b, ptr nocapture %c) nounwind {

3 entry:

%0 = xor i1 %a, %b

4

br i1 %0, label %if.end, label %if.then

if.then:

call void %c() #1

8

br label %if.end

9

10

11 if.end:

ret void

12

13 }

```

Listing 2.1: LLVM IR example

The set of available machine instructions is defined in the ISA. The following subsections discuss various instruction selection strategies.

#### **Macro Expansion**

With this instruction selection technique, multiple templates are defined. A template can be the assignment of a variable or an operation performed on one or more operands, which can subsequently be expanded. The selector traverses the program's IR elementwise and emit the corresponding assembly code when a template is matched [Hjo16], p13]. An example is shown in Listing [2.2] from [Hjo16], p13]. The snippet shows C statements, where each statement is translated into a sequence of machine instructions. The selected machine instructions are written as comments. The example represents just a high-level idea.

```

int a = 1;  // mv r1, 1

int b = a + 4; // add r2, r1, 4

p[4] = b;  // mv r3, @p

// add r4, r3, 16

// st r4, 0(r2)

```

Listing 2.2: Macro Expansion Example from [Hjo16, p13]

The macro expansion has limitations regarding the code quality and performance  $\overline{\text{DF84}}$ . A peephole optimizer goes over the emitted machine instructions and tries to combine multiple instructions into one machine instruction. An  $\overline{\text{IR}}$  is expanded into sequence of register transfer lists RTL. This representation is close to an assembly representation. The peephole optimizer's combiner then runs over the RTL and tries to combine them into a

larger RTL. Each target-machine's instruction also has a RTL. The combiner tries to merge the program's RTL expressions into one which corresponds to an instruction's RTL.

Equation 2.1 shows the example for a RTL in Hjo16, p23]. The add instruction has two observable effects. The first is the result of an addition with an immediate value and the second observable effect is the write to a status flag. As also noted in Hjo16, p23], the effect on the status flag is only relevant when a subsequent instruction reads the flag. If no other instruction reads the flag then it becomes unobservable. Hence, it can be removed which increases the chances to be combined into a larger RTL which might lead to performance gains.

$$RTL(add) = \left\{ \begin{array}{l} r_d = r_s + imm \\ Z = (r_s + imm) \iff 0 \end{array} \right\}$$

(2.1)

A popular compiler framework, GNU Compiler Collection (GCC), uses macro expansion together with a target-independent peephole optimizer. The GCC's low-level IR, known as Register Transfer Language, is a LISP-like language. A particular node is called Register Transfer Language Expression in the IR. GCC transforms a program into RTL and finally applies the RTL Optimizer to improve the generated code. GCC's instruction selector is a modified version of the Davidson-Fraser approach that was presented above DF04 [Anod].

#### Tree Covering

Another approach for instruction selection is called tree covering. As already mentioned, some IRs can be in tree form. When both instruction patterns and IR are represented as trees, they can create a cover of the IR tree. Since multiple instruction patterns may cover the same IR tree, only patterns from the minimal cost cover should be considered. An optimal solution can be computed in linear time using bottom-up dynamic programming Hjo16, p58].

In AGT89, Twig was introduced as a tree-based notation for implementing code generators. First, the algorithm builds a top-down tree automaton from instruction patterns. Cost computation is based on Aho and Johnson's dynamic programming algorithm, which computes a program cover by selecting a set of pattern trees [Hjo16, p58]. That is because many covers overlap, and it is desired to get the cover with the minimal costs.

Restrictions. However, tree covering comes with multiple restrictions. First, dataflow is usually not represented as tree, but generally as Directed Acyclic Graph (DAG). A DAG is a graph with directed edges which has no cycles. Compared to a tree, a DAG may have multiple roots. Second, common subexpressions cannot be modeled [Hjo16, p76]. Unfortunately, tree covering is limited to tree patterns.

#### **DAG** Covering

Both the IR and the instruction selector may have different representations. There are three different cases to distinguish:

- 1. Section 2.2 discusses the case when the IR and the instruction selector are trees.

- 2. An IR can be a DAG and the instruction selector is a tree.

- 3. Another case is when IR and the instruction selector are both DAGs.

Unfortunately, the most interesting case is the third case and such a covering cannot be found optimally since it is NP-complete [Hjo16], p78]. In [Ert99] [TEK18], Ertl shows that an optimal selection can be achieved by extending tree parsers for [IR DAGs], but the approach fails to produce optimal results in all cases.

In [Hjo16], p84], the process of "undagging" a DAG is described, where "undagging" refers to converting a DAG into a set of separate trees by splitting edges at points where common subexpressions occur. Afterwards, tree covering algorithms can be applied to each extracted tree. A common subexpression is easily detectable because two adjacent nodes have multiple edges between them.

Instruction selection can also be formulated as *Partioned Boolean Quadratic Problem* and solved efficiently for large instances Ebn+08. We refer to Hjo16 where other DAG covering approaches are presented.

#### **TableGen**

LLVM uses a domain-specific language called TableGen to concisely define structured data. The two main data structures are records and classes. Records are concrete instances of definitions, while classes are blue prints for records. To create a record the keyword def and for a class the keyword class are used. Within a record, each entry is a key-value pair. Classes predefine key-value pairs which can be overwritten when a record inherits from the class. TableGen is used by different generators, where each definition represents a specific instance of an entity. TableGen is used for the following use cases: [Ano24]

- 1. Instruction definitions

- 2. Register definitions

- 3. Calling conventions

- 4. Command-line options

- 5. Diagnostic messages

TableGen is statically typed and supports bit, int, string, bit vector, list, direct cyclic graph as primitive types. The DAG type is mainly used for instruction selection definitions. TableGen also allows embedding C++ code at certain positions.

In Listing 2.3, the instruction ADDI defines multiple key-value pairs. The OutputOperandList sets the output operands. Likewise, InputOperandList defines the input operands. ADDI takes one register and an immediate as input operands. The let Inst... statements define the mapping from the operands to the instruction's binary representation. LLVM uses many target-independent passes that operate on target-machine instructions. These passes check the machine instruction flags and enable optimizations if applicable.

Listing 2.4 presents an instruction selection pattern in TableGen with two components. The first is the instruction selector that defines a tree pattern for the instruction selection. In this example, the root of the instruction selector graph is the add node, representing the LLVM IR addition operation in the Selection DAG Instruction Selection's Directed Acyclic Graph (SelectionDAG). The SelectionDAG is presented in Section 2.2. The selector's root has two children: an input register from register file X and the immediate value simms. The second part specifies which machine instruction to emit. In Listing 2.4, the RISC-V ADDI instruction is emitted with operands matching those of the instruction selection pattern. The destination register is modeled implicitly because the ADDI record has an OutOperandList that defines the output as a register from the register file X.

Listing 2.3 shows an example instruction definition. In this case, RV3264Base\_ADDI\_immSAsInt64 serves as the immediate operand for the ADDI instruction. This operand inherits from a class, which sets the EncoderMethod and DecoderMethod. The EncoderMethod is a C++ function that encodes the immediate operand into the binary representation. Similarly, the DecoderMethod is a C++ function that decodes the binary representation of an immediate operand. The DecoderMethod corresponds to the field access function defined in VADL.

Listing 2.4: Instruction Selection Pattern with TableGen (SDISel)

#### LLVM's Instruction Selectors

LLVM provides multiple instruction selectors that compiler backend engineers can use. The oldest selector is Selection DAG Instruction Selection (SDISel). It is limited to a selection based on basic blocks and single instructions. A faster selector is Fast Selection DAG Instruction Selection (FastISel) and the latest development is Global Selection Dag Instruction Selection (GlobalISel). The latest allows matching the entire function's scope. The following three sections explain the currently supported instruction selectors in LLVM. However, FastISel belongs to SDISel because it is embedded in it. It is possible to fallback from FastISel to SDISel in the middle of the basic block. This is not possible

```

1 // Defines a parameterized blueprint for the ADDI's immS

2 // immediate value.

class RV3264Base_ADDI_immS<ValueType ty> : Operand<ty>

// C++ method to encode the value into the

// binary representation.

let EncoderMethod = "RV3264Base_ADDI_wrapper";

// C++ method to decode the value from the

// binary representation.

let DecoderMethod = "RV3264Base_ADDI_immS_decode_wrapper";

11 }

12

13 // Concrete instance of ADDI's immS with a predicate function.

14 def RV3264Base_ADDI_immSAsInt64

: RV3264Base_ADDI_immS<i64>

, ImmLeaf<i64,

16

[{ return RV3264Base_ADDI_immS_predicate(Imm); }]>;

17

19 // Concrete machine instruction for addition with register

20 // and immediate.

21 def ADDI : Instruction

22 {

23 // Output operands of the machine instruction.

24 let OutOperandList = ( outs X:$rd );

25 // Input operands of the machine instruction.

26 let InOperandList =

ins X:$rs1, RV3264Base_ADDI_immSAsInt64:$immS );

28 // Encodings of the binary representation.

29 field bits<32> Inst;

30 bits<7> opcode = 0b0010011;

31 bits<3> funct3 = 0b000;

32 bits<64> immS;

33 bits<64> rs1;

34 bits<64> rd;

35 // Mappings of the instruction's operand into the binary

36 // representation.

37 let Inst{31-20} = immS{11-0};

38 let Inst{19-15} = rs1{4-0};

39 # ...

40 // Machine instruction flags that are used in the

41 // target-independent optimizations.

42 let isTerminator

= 0;

43 let isBranch

= 0;

44 # ...

45 // Hardware registers that are being read from by the instruction.

46 let Uses = [ ];

47 // Hardware registers that are overwritten by the instruction.

48 let Defs = [ ];

49 }

```

Listing 2.3: Instruction Definition TableGen for ADDI

between GlobalISel and SDISel. A fallback from GlobalISel restarts the selection from the beginning Col25, p385].

According to Col25, p385], instruction selection follows three phases. First, the translation of the LLVM IR into a separate IR. Second, the legalization of IR constructs that are not supported by the target-machine. For example, a compiler frontend might produce an LLVM IR which relies on multiplication, while the target-machine does not support it. These differences need to be handled by replacing LLVM IR instructions with legal operations. Finally, the selection phase handles the translation from the selector's IR to the target-specific machine IR of the compiler backend.

#### SelectionDag

As already mentioned above, an optimal DAG covering is NP-complete. The SDISel splits each basic block into separate DAGs and starts the following process: Col25, p391 Hjo16, p81

- 1. **SelectionDAGBuilder.** Initially, the LLVM IR needs to be translated into selection nodes called Selection Directed Acyclic Graph Node (SDNode) in the SelectionDAG. It is also possible to define custom nodes which can be matched later. However, they have to be replaced in a later stage.

- 2. **DAGCombine.** LLVM provides many optimizations that can be done on the SDNodes. The *DAGCombiner* fuses multiple nodes together when it can find a more efficient representation. These optimizations are target-independent. But, the compiler backend can also apply multiple target-dependent optimizations to combine SDNodes. This DAGCombine pass is run before the pre-legalization. Therefore, it will have nodes with types and operations which are not supported by the target-machine.

- 3. **Legalize.** The legalizer converts an illegal IR into a legal IR. Hence, the DAG will only contain types and operations that are supported by the target-machine.

- 4. **DAGCombine.** The DAGCombiner is run again and applies optimizations on the DAG but after the legalization.

- 5. **Selection.** Finally, the instruction selection is invoked and the SDNodes are mapped to machine IR.

- 6. **Schedule.** The last step is the scheduling which linearizes the sequence to create a machine basic block. A machine basic block contains only machine instructions, as all operations have been replaced accordingly.

At LLVM's compile time, the instruction definitions and instruction selection patterns defined in TableGen are translated into C++ code. According to Ben, the instruction selection patterns are compiled into some kind of "byte code". All of these are stored in the *MatcherTable*. The instruction selector executes the entries one at a time. If an opcode, predicate, or type does not match, it skips entries to match the next pattern.

If all entries are exhausted and no match is found, the compiler throws a selection error, and the compilation stops. According to [Hjo16], p81], this approach is a greedy IR-DAG-to-DAG rewriter. It is referred to as a rewriter because a match on the DAG IR is replaced by a machine instruction tree. Therefore, a tree pattern matching is used for instruction selection.

Upstream compiler backends include peephole passes for more complex patterns. Upstream compiler backends are officially available LLVM compilers. A downstream compiler backend uses LLVM but is not part of the main LLVM project. An example of a peephole pass in the upstream AArch64 compiler backend is the AArch64LoadStoreOpt pass. The AArch64 ISA supports load and store memory instructions that can pre- or post-increment a pointer. These instructions cannot be modeled by tree patterns because the patterns would have multiple roots. The peephole pass iterates over the machine instructions after the instruction selection and fuses multiple instructions into a single machine instruction.

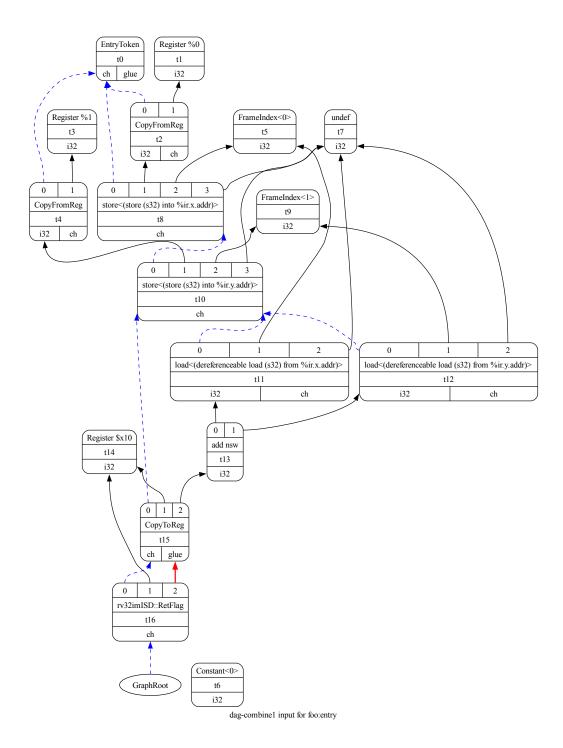

Listing 2.5 shows the LLVM IR for a function that takes two integers, adds them, and returns them. The example shows multiple register spills to the stack that are optimized when the IR is compiled with higher optimization levels. Figure 2.1 represents the code in Listing 2.5 before the DAG combine. There are three different kinds of nodes in the graph: data nodes, scheduling nodes, and glue nodes. Data nodes represent operations and values that are computed, scheduling nodes represent the order in which computations occur, and glue nodes enforce that specific instructions must be scheduled immediately after each other. Since the SelectionDAG is a DFG, the black edges represent use-def dependencies. The blue-dashed edges represent scheduling dependencies between nodes that enforce an ordering between the source and target nodes. Finally, glue dependencies indicate that it is important that two instructions stay together and are marked with red edges. This requirement is stricter than scheduling dependencies. Nodes with a glue dependency must stay together Ano25a.

The numbers on the top of some nodes indicate the operand of the operation. The node's bottom row represents the results. Nodes may return multiple values. The type i32 defines the resulting type as a 32-bit signed integer. The chain operand ch defines an ordering constraint between source and target node. EntryToken indicates the beginning of a basic block. The graph's root is the last instruction in the block. CopyFromReg and CopyToReg model data flow between basic blocks.

#### **Fast Instruction Selection**

The benefit of using FastISel is faster compilation time. Some SDISel patterns are automatically translated for FastISel. However, it comes with restrictions. Col25, p464 lists advanced selection patterns that are not supported. Two unsupported patterns are special matching functions. The third, a ComplexPattern allows custom matching functions written in C++. In AArch64, the immediate operand of an addition can be shifted. In the upstream implementation, the addition's immediate operand is merged

Figure 2.1: SelectionDAG for Listing 2.5

Listing 2.5: LLVM IR for a function with two inputs which are added and the result is returned

into a single *complex* operand, combining the value and the shift operands. The matching logic for handling the merged operand is manually done in C++. However, this is not automatically supported by FastISel unless it is implemented explicitly [Col25], p468].

#### Global Instruction Selection

The GlobalISel is an alternative instruction selection in LLVM that is considered to be a natural successor of SDISel. While SDISel operates at the basic block level, GlobalISel considers the entire function. A benefit of GlobalISel over SDISel is the RegBankSelect pass. While a register class groups registers by register file, a register bank is a functional group of registers. For instance, a register bank is the set of integer registers in the entire processor. A cross-register bank copy moves data from a general-purpose register to a vector register. It is preferable to avoid copying between register banks. Both SDISel and FastISel do not consider register banks [Col25], p454].

The following algorithm is documented by [Col25, p391] and [Anoa].

- 1. IRTranslator. GlobalISe has its own selection IR which is called Generic Machine Intermediate Representation (gMIR). This step translates the LLVM IR into gMIR Anof.

- 2. **Legalizer.** It shapes the gMIR into a representation that is supported by the backend Anog.

- 3. **RegBankSelect.** This pass constraints registers in gMIR to some register bank. This is useful when the backend supports multiple register files, then it avoids the copying between those Anol.

- 4. **Select.** Finally, the gMIR is transformed into a representation which is target-specific. It starts at the bottom of the machine function and walks up to the definition Anoel.

GlobalISel's selection pass is traversing over all the machine function's basic blocks in post-order. It then iterates from the end to the beginning of the function through all the gMIR instructions. The goal is to find a pattern which matches the gMIR. If the match was successful, it is mapped to a Machine Intermediate Representation (MIR). MIR is the low-level representation above the actual machine code. This greedy approach does not correspond to a DAG or tree covering, but is a one-to-one mapping. So then why is it called global? GlobalISel also includes a combiner which matches and fuses instructions together. Therefore, the scope on which the combiner operates is the entire function Anoel.

The selection with the matcher table's byte-code remains the same as for SDISel,

#### 2.1.3 Instruction Scheduling

According to [Hsu25], the machine scheduler has two objectives. It has to make the best use of the target machine's resources, while keeping the register pressure low. Especially for in-order micro architectures, instruction scheduling is important because it can improve the instruction-level-parallelism by reordering instructions [Col25] p491]. According to LLVM's documentation in llvm/include/llvm/CodeGen/MachineScheduler.h, the default scheduler is a list scheduler that updates the instruction stream, register pressure, and live intervals [Coo12] p634]. Subtargets can then choose a scheduling policy and a register-pressure-tracking policy. A scheduling policy is the direction of the scheduling. The top-down approach selects the next node with no successors. On the other hand, the bottom-up approach selects the next node with no predecessor. In other words, the top-down approach considers nodes from the beginning of the block first, while the bottom-up approach starts the scheduling from the last instruction of the basic block. Bidirectional is a mixture of both approaches, where the scheduler can schedule an instruction after all its successors or predecessors have been scheduled [Hsu25].

#### 2.1.4 Register Allocation

LLVM uses LLVM IR as the intermediate representation of a program. This IR is in SSA RB22. LLVM IR assumes that there is an unlimited number of registers. Target machines, however, have only a restricted number of hardware registers. We also use the term *physical register* as a synonym. The register allocator assigns each virtual register a hardware register. Since there are more virtual registers than hardware registers, each hardware register is assigned to hold the values of multiple virtual registers. The allocator must compute the live ranges of each virtual register. A virtual register is considered dead when it has no usages and marks the corresponding hardware register as available. In many cases, there are more virtual registers alive than there are free hardware registers available. For these cases, the compiler stores the value temporarily in memory. This is called spilling. After the value is saved, the physical register can be reassigned. The previously stored value is not lost. When the old value is needed, it can be reloaded from memory. However, this is costly because accessing memory takes many cycles longer than accessing a register.

Register allocation maps virtual registers to hardware registers and determines which hardware registers are spilled. Spilling introduces new stores and loads, which influence instruction scheduling. Likewise, instruction scheduling can change register live ranges and influence register allocation.

There are multiple register allocation schemes, however, the two most prominent techniques are graph coloring and linear scan Cha82 PS99. LLVM supports several register allocation algorithms Anom. The fast register allocator is the default for debug builds and does the register allocation per basic block. The pbqb (Partioned Boolean Quadratic Programming) allocator uses a PBQB solver to construct a solution HKS03. The basic allocator is useful for debugging issues. The greedy register allocator is the default allocator and is based on the previously mentioned basic allocator. Overall, it tries to minimize the cost of spill code. According to Ole11, the greedy allocator tries to allocate large live ranges first. Small live ranges are allocated with the remaining set of registers. Live ranges of variables that do not fit are not spilled immediately. Instead, the live range is split. Thus, the range narrows and spilling becomes less likely.

#### 2.2 Processor Description Languages

Design Space Exploration (DSE) for ASIPs is time-consuming and difficult, but necessary to accelerate a particular application. Additional machine instructions distinguish an ASIP from a general-purpose processor. However, custom hardware requires custom tooling, which slows iteration as each change requires updating the toolchain and simulators. This is a major challenge for ASIP designers and introduces a dependency between hardware and software. This dependency is called hardware-software codesign problem.

PDLs are designed to address the hardware-software codesign problem. A PDL is a language for describing a processor architecture. Thus, it is designed to generate a compiler, a simulator and a specification in a Hardware Description Language (HDL). The specification becomes the *source of truth*. Karuri et al. describe such a design flow in detail in Kar+08. However, their processor was intended to be only partially configurable. In Hoh+04, Hohenauer et al. show how to model Infineon PP32 and ST200 microcontrollers. Scharwaechter et al. present a case study for IPSec encryption with ASIPs in Sch+07. Both articles used the PDL LISA.

PDLs are classified into two categories: specification-based or template-based [KL11], p8, p38]. A specification-based PDL is a high-level language that abstracts low-level details away, allowing only a limited degree of freedom. While for template-based specifications, Karuri and Leupers create two categories for customization. First, processor customization is achieved by combining existing features. Second, a PDL allows the specifier to add additional features.

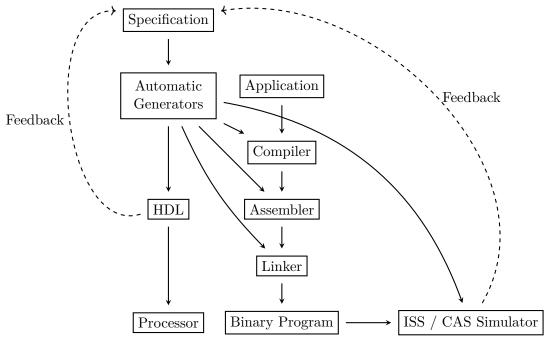

Figure 2.2: Specification based ASIP design flow from KL11, p40

Figure 2.2 shows an overview of a specification-based design flow for ASIPs from KL11 p40. The specification is used as an input for automatic generators. HDL specification, Compiler, Assembler, Linker, Instruction Set Simulator and Cycle Accurate Simulator were generated by automatic generators. The graph depicts two design flows.

- 1. The first design flow starts with the specification and ends with the specification in a HDL. The specification in the HDL can be synthesized into a processor. But during the DSE, feedback from the synthesis is incorporated into the processor specification.

- 2. The second design flow begins with the specification and generates the compiler, assembler, and linker. The toolchain's output is an executable, which is the input for the simulators. The feedback is incorporated into the specification based on the simulation results.

This process highlights the DSE because the specification is iteratively updated until the design meets specific constraints and exploration is complete. For embedded computing, energy efficiency, cost and size are key constraints that are opposed to each other and require trade-offs.

Listing 2.6: RISC-V's ISA in VADL

#### 2.3 Vienna Architecture Description Language

VADL is a language for describing processor architectures Fre+. It is structured into multiple sections to avoid *leaky abstractions*. An abstraction is leaky when low-level details have to be considered in high-level designs. The writer specifies a specification with separate ISA, Application Binary Interface (ABI), and Micro Architecture (MIA) sections. VADL was implemented by two projects. The latest and only active development is OpenVADL. Based on the given specification, OpenVADL generates multiple *artifacts*. An artifact is the compiler toolchain, Instruction Set Simulator (ISS), or a synthesizable processor in a HDL. The following sections present an overview of VADL.

#### 2.3.1 Instruction Set Architecture

An ISA defines the supported machine instructions by the specified ASIP. An example of such a specification is listed in Listing 2.6. The keyword **instruction set** architecture defines a new ISA. ISAs are extensible, which is indicated by the extending keyword. The keyword using defines a type alias. The program counter defines a special purpose register that holds the memory address of the next instruction to be executed. The keyword register introduces a new register file called X. In this specification, the X register file consists of multiple registers, each addressed by a unique 5-bit index, and each register can store a 32-bit value.

An instruction has a type that is called *format*, and a format is created with the keyword **format**, as shown in Listing 2.7. The format defines an ordered list of fields, each with one or more bits. At the end of the format, a field access function, immS = imm as SInt<32>, is provided. This field access function serves as a separation between the instruction's behavior and its decoding. The instruction's behavior is explained in Section 2.4.1. By moving the decoding computation to the field access function, the reader can assume that the behavior operates on the decoded values, which increases readability. Applying the immS function in the instruction's behavior is exactly the same as reading the imm field, but with a sign extension.

```

1 format Itype : Inst =

// [31..20] 12 bit immediate value

2 { imm

: Bits<12>

: Index

// [19..15] source register index

rs1

funct3 : Bits<3>

// [14..12] 3 bit function code

: Index

// [11..7]

destination register

rd

opcode : Bits<7>

// [6..0]

7 bit operation code

= imm as SInt<32> // sign extended immediate value

8 }

```

Listing 2.7: RISC-V's Itype instruction format in VADL

```

instruction ADDI : Itype =

X(rd) := (X(rs1) as SInt + immS as SInt) as Regs

encoding ADDI =

{ opcode = 0b001'0011

, funct3 = 0b000

}

r assembly ADDI = (mnemonic, " ", register(rd), ",", register(rs1),

",", sdec(imm as SInt<12>))

```

Listing 2.8: RISC-V's ADDI instruction in VADL

Figure 2.8 shows the *ADDI* instruction, which has the *Itype* format. The instruction has three components. The first is defined with the keyword **instruction** and implements the behavior. Next is the **encoding** that sets the bit fields for the **opcode** and **funct3**. The remaining fields rs1, rd, and imm are instruction operands and have no fixed bit representation. The third is the **assembly** keyword, which specifies how the compiler has to print the instruction in assembly. The function **register** maps a numeric value to a register file, e.g., *X10*. The other function **sdec** prints the value of the encoded field imm as a signed decimal number. **udec** can be used for unsigned decimal values and **hex** for signed hexadecimal representation.

Listing 2.9 shows an encoding function and a predicate function. An encoding function is the inverse function of the field access function. The terms decode function and field access function can be used interchangeably. The predicate function is a boolean function that determines whether a value is within range during instruction selection. In this particular case, immS must be in the range -2048 and 2047 to be selectable. Otherwise, the instruction selector has to select another instruction. Why was it not necessary to define these functions in Listing 2.7? We refer the reader to Section 3.3 for the documentation on the function's generation. But the short answer is that the compiler generator can automatically derive encoding and predicate functions from field access functions of a certain form.

```

1 format Itype : Inst =

// [31..20] 12 bit immediate value

2 { imm

: Bits<12>

: Index

// [19..15] source register index

3 , rs1

funct3 : Bits<3>

// [14..12] 3 bit function code

rd

: Index

// [11..7]

destination register

// [6..0]

opcode:

Bits<7>

7 bit operation code

imm as SInt<32> // sign extended immediate value

immS

immS(11..0)

// encoding function

9 ,

immS

immS >= -2048 && immS <= 2047 // predicate function

10 }

```

Listing 2.9: RISC-V's Itype instruction full format in VADL

#### Registers

Listing 2.10 shows the declaration of registers in the AArch64 specification in VADL. The main register file is S. It has the type Index -> Bits<64>. The type is a function with 5 bits as an argument and returns 64 bit values. Therefore, the number of registers is 32. The X register file is an alias because it was created with the **alias register** keyword. The W register file is also an alias of X, but the type indicates that each register in W references only the lower 32 bits of a register in X.

The annotation [zero : X(31)] declares that X(31) is the zero register. The annotation **overwrite source** defines the zero extension of a subregister from W during writes. An alias has to be defined in AArch64 because it is possible to address the 32 least significant bits from a register in register file S.

Both LR and SP are aliases for a concrete register in S. Additionally, we define the status registers  $NZCV\_N$ ,  $NZCV\_Z$ ,  $NZCV\_C$ ,  $NZCV\_V$ .

The importance of aliases becomes clear for two reasons. First, they can be constrained. For example, in Listing 2.10, reading from registers S(31) and S(31) return different values because the alias S(31) has the zero annotation. The second reason is the definition of subregister relationships, explained in Section S(3.9).

#### Relocations

Generally, program compilation has two stages. Each source code file is compiled into an object file. Afterwards, object files are linked to create a single executable. This process creates challenges for jumps and global variables. Jump instructions change the Program Counter (PC) to set the address of the next instruction. However, the function's address in the final executable is not determined at compile-time yet. Assemblers use placeholders in object files. The linker updates these placeholders because the addresses are known at link-time. These placeholders are called relocations.

The keyword **relocation** creates a custom relocation in VADL, as shown in

```

S : Index -> Bits<64>

1 register

2 [zero : X(31)]

3 alias register X = S

[zero : W(31)]

5 [overwrite source: zero]

6 alias register W = X(*)(31..0)

7 alias register SP : Address = S(31)

8 alias register LR : Address = S(30)

10 [negative status register]

11 register NZCV_N : Bits<1>

// Negative

12 [zero status register]

13 register NZCV_Z : Bits<1>

// Zero

14 [carry status register]

15 register NZCV_C : Bits<1>

// Carry

16 [overflow status register]

17 register NZCV_V : Bits<1>

// Overflow

```

Listing 2.10: Register definition for AArch64 in VADL

Listing 2.11. The **syntax** annotation declares how the relocation is printed in the assembly representation. Brackets mark placeholders, which the compiler later replaces: the first for the relocation name, the second for the label name.

VADL supports different types of relocations that are differentiated by their annotation. For example, **relative** creates a relative relocation, while **global offset** creates a global offset relocation. Both hi and lo are absolute relocations. With absolute relocations, the linker directly updates the placeholder with the computed value. For relative relocations, the PC is subtracted from the computed value. Additionally, got\_pcrel\_hi applies to relocations involving the global offset table. The global offset table is necessary for compilation with position-independent code. VADL supports relocations for only one value.

#### 2.3.2 Application Binary Interface

According to the Swift Stability Manifesto Inc: "[...] ABI is Application Binary Interface, or the specification to which independently compiled binary entities must conform to be linked together and executed. These binary entities must agree on many low level details: how to call functions, how their data is represented in memory, and even where their metadata is and how to access it."

To conclude, an ABI is a contract to ensure compatibility of binary entities between different toolchains.

```

1 [syntax : "%{}({})"]

2 relocation hi( symbol : Bits<32> ) -> UInt<20> =

( ( symbol + 0x800 as Bits<32> ) >> 12 ) as UInt<20>

5 [syntax : "%{}({})"]

6 relocation lo( symbol : Bits<32> ) -> SInt<12> =

symbol as SInt<12>

9 [relative]

10 [syntax : "%{}({})"]

relocation pcrel_hi( symbol : Bits<32> ) -> UInt<20> =

( ( symbol + 0x800 as Bits<32> ) >> 12 ) as UInt<20>

12

14 [relative]

15 [syntax : "%{}({})"]

relocation pcrel_lo( symbol : Bits<32> ) -> SInt<12> =

(symbol + 4) as SInt<12>

17

18

19 [global offset]

20 [syntax : "%{}({})"]

21 relocation got_pcrel_hi( symbol : Bits<32> ) -> UInt<20> =

( ( symbol + 0x800 as Bits<32> ) >> 12 ) as UInt<20>

```

Listing 2.11: Relocations for RISC-V in VADL

Listing 2.12 shows an ABI example for the ISA RV32IM. An ABI is created using the keyword application binary interface. size\_t type defines size\_t type in C, and for RISC-V, it must be unsigned. alias register sets names for assembly printing. Without an alias, it's unclear how to print a register from a register file. The different registers stack pointer, return address, global pointer, frame pointer, and thread pointer declare reserved registers. These are excluded from register allocation. special return instruction and special call instruction set instructions for function calls and returns.

special local address load instruction, special global address load instruction, and special absolute address load instruction load addresses. Multiple instructions allow the distinction between position-independent and non-position-independent code.

The **return value** defines registers for return values from functions. **function argument** specifies registers for passing values to function calls. **caller saved** and **callee saved** define the calling conventions.

Listing 2.12 also contains three **constant sequence** and one **register adjustment sequence**. A constant sequence is an internal pseudo instruction for the constant

materialization. A pseudo instruction expands into several machine instructions, but it improves the readability in the assembly. Internal pseudo instructions are used by the compiler and are not printed in the assembly. Constant materialization builds a constant using machine instructions. The three sequences differ by type and size. It is more efficient to use one *ADDI* instruction if the immediate fits in its encoded field. Unlike a **constant sequence**, a **register adjustment sequence** takes an extra register argument. It adjusts a value instead of overwriting it. Register adjustment sequences are useful for stack adjustments, as a program must not overwrite the original stack pointer.

## 2.4 OpenVADL

OpenVADL is the main implementation of VADL Fre+26 Fre+. The previous implementation is called Original VADL. However, it was an internally developed project and is not publicly available. Fre+ describes the differences between the original implementation and OpenVADL in more detail. OpenVADL is its natural successor. A major difference between the two is the design of the IR. In addition, all generators were reimplemented from scratch. Previously, the ISS was a self-contained project, but it is now implemented on top of QEMU Bel05. The original and OpenVADL's compiler generator are both based on LLVM. However, the reimplemented generator is more advanced and supports higher optimization levels.

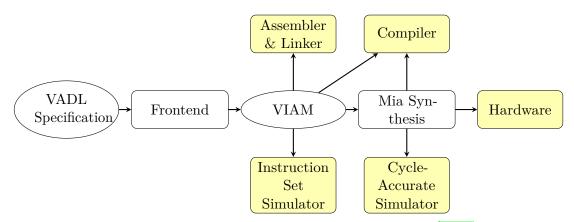

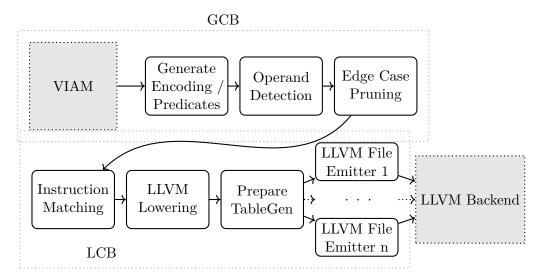

Figure 2.3 shows an overview of the architecture. Yellow boxes represent generators. The specification is parsed by the frontend, which expands all macros and creates an AST. Afterwards, the AST gets transformed into the VADL Intermediate Architecture Model (VIAM), OpenVADL's IR. All generators depend on the VIAM and modify its graph as needed. The generated compiler can be built without knowledge of the microarchitecture. The compiler generator is split into two components: Generic Compiler Backend Generator (GCB) and LLVM Compiler Backend Generator (LCB). The initial idea was to support multiple compilers with OpenVADL. We tried to move common functionality into a generic and reusable component. Nonetheless, LLVM is currently the only compiler supported by OpenVADL. The compiler generator is called LCB and sits on top of GCB. In reality, the GCB is a thin layer and design decisions were heavily influenced by LLVM.

### 2.4.1 VADL Intermediate Architecture Model

Our observation was that multiple generators require different representations. However, all the generators rely on control flow and dataflow. The VIAM serves as IR in OpenVADL where the instruction's behavior is modeled as a graph. Each generator tailors the IR to its needs by replacing or extending nodes in the graph. The compiler generator operates mostly on the instruction's behavior graph. The VIAM's instruction behavior graphs combine both control flow and dataflow into one multi-graph. Each behavior graph contains a start and an end node. The end node contains a list of side effects. Each side effect is a node in itself. For example, writing a register file is a side-effect node that has two inputs. One input is the destination index in the register file, where the write is performed. The

```

application binary interface ABI for RV32IM = {

size_t type = unsigned int

pointer align = 32

alias register zero = X(0)

alias register ra = X(1)

alias register sp = X(2)

alias register gp = X(3)

8

alias register tp = X(4)

9

10

// ...

11

stack pointer = sp

12

return address = ra

13

global pointer = gp

14

frame pointer = fp

thread pointer = tp

16

17

special return instruction = RET

18

special call instruction = CALL

19

special local address load instruction = LLA

20

special global address load instruction = LGA_32

special absolute address load instruction = LA

23

return value = a{0..1}

24

function argument = a\{0...7\}

25

26

// ra is callee saved because it is used as

27

// normal register and has to be restored.

28

caller saved = [a\{0...7\}, t\{0...6\}]

29

callee saved = [ ra, s{0..11} ]

31

constant sequence( rd : Bits<5>, val : SInt<32> ) =

32

33

LUI { rd = rd, imm = hi( val ) }

34

ADDI { rd = rd, rs1 = rd, imm = lo(val) }

35

}

36

37

constant sequence( rd : Bits<5>, val : UInt<32> ) =

38

39

LUI { rd = rd, imm = hi( val ) }

40

ADDI { rd = rd, rs1 = rd, imm = lo(val) }

41

}

42

43

constant sequence( rd : Bits<5>, imm : SInt<12> ) =

44

45

ADDI{ rd = rd, rs1 = 0, imm = imm }

46

47

48

49

register adjustment sequence

50

( rd : Bits<5>, rs1: Bits<5>, imm : SInt<12> ) =

51

ADDI{ rd = rd, rs1 = rs1, imm = imm }

52

}

53

54 }

```

Listing 2.12: ABI section in VADL for RV32IM

Figure 2.3: Overview of OpenVADL Compiler Architecture from [Fre+]. Yellow boxes represent generators.

other input is the value that is written. Reading from a register file and reading from a concrete register are modeled as single node that references the underlying resource. Dataflow is implicitly modeled in SSA form due to the semantics of let statements. All reads must precede all writes, and all writes are executed at the end of the block Fre+.

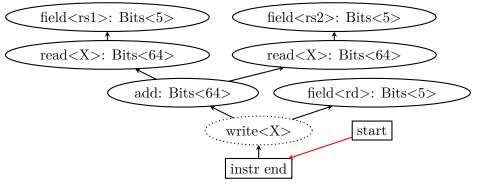

Figure 2.4 shows an example of a RISC-V ADD instruction from Fre+. The write < X > is the side effect of the instruction, which has two inputs. One input is the value which is written, namely the add: Bits < 64 >. The second input is the node field < rd >, which specifies where the value is written. The addition node is itself integrated as an operation in VADL. They are also called Builtins. This thesis uses the terms builtin and operation synonymously. The builtin set is predefined and cannot be extended by the specifier. Each generator can modify this representation by adding, removing, or replacing nodes.

Figure 2.4: VIAM behavior graph of the RISC-V ADD instruction from Fre+

The VIAM has multiple types of nodes, such as:

- BuiltinNode. This node represents an operation like addition or a shift in the graph.

- ReadRegTensorNode or WriteRegTensorNode. This node models a read from or write to a register or a register file. It contains a reference to the underlying resource.

- ReadArtificalResourceNode or WriteArtificialResourceNode. An artifical resource is an alias to a register or register file.

- ReadMemoryNode or WriteMemoryNode. This node models the access to memory.

- SelectNode. A SelectNode is a conditional node that represents the selection of one of multiple input values based on a boolean condition input.

- IfNode. A IfNode is control-flow node that models the execution based on a boolean condition.

- FieldRefNode. This node represents the access to a field in a format.

- FieldAccessRefNode. This node represents the call to a field access function, defined in the format.

- SideEffectNode. The SideEffectNode is a term for a group of nodes that write a resource in the VIAM.

### 2.4.2 Semantic Gap

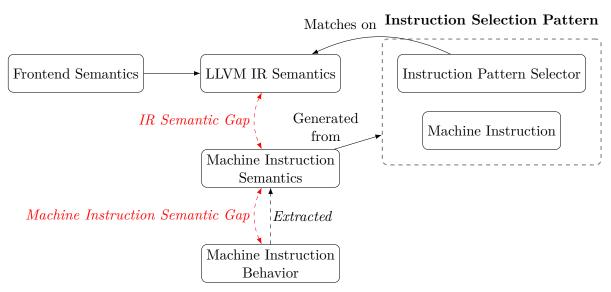

Generally, compilation of programs begins by translating source code into an IR, which is then translated into machine instructions. Figure 2.5 shows a compilation flow overview. The term *semantics* refers to the meaning of operations at each stage. A programming language first defines frontend semantics for operations such as addition. Next, LLVM IR provides its own IR semantics for this operation. Finally, machine instructions have specific semantics as well. As described in Section 2.1.2, instruction selectors match operations on the SelectionDAG or gMIR which are mapped from LLVM IR. However, the compiler generator must generate instruction selection patterns from the machine instruction behavior graphs specified in a VADL specification.

The semantic gap refers to the differences or mismatches between different semantics. The Machine Instruction Semantic Gap is the difference between what an instruction is supposed to do (semantics) and what the hardware actually executes (behavior). The IR Semantic Gap exists because compilers allow undefined behavior. Instructions like division have corner cases, such as division by zero. Undefined behavior allows the compiler to ignore corner cases Anoh. However, the machine instructions implement behavior by raising an exception or computing an invalid value. When generating instruction selection patterns, the compiler generator must bridge the gap between undefined and defined behavior, which we refer to as IR Semantic Gap.

Additionally, instruction behavior is specified with VADL operations and there is no one-to-one mapping between LLVM IR instructions and VADL operations. For instance, VADL includes an operation for addition that sets the status flags, whereas LLVM IR does not. In this work, we use the term *semantic gap* to summarize the *Machine Instruction Semantic Gap* and the *IR Semantic Gap*.

Figure 2.5: Semantic Gap in OpenVADL

# Implementation

The following sections discuss the implementation details of the automatic generation of a compiler, which is the main contribution of this thesis.

## 3.1 Research Questions

**RQ1:** How can conditional branch instructions be automatically derived from a processor description language?

Section 3.6 presents a classification algorithm that defines static properties for the behavior graphs of machine instructions in the VIAM. The algorithm assigns a classification label to each matched machine instruction when certain properties are fulfilled. For example, RISC-V has a single instruction that compares two registers and adjusts the PC based on the comparison. By contrast, AArch64 uses two separate instructions. First, a compare instruction compares two registers and sets the CPU flags depending on the result. The second instruction is a jump that interprets the CPU flags and updates the PC. These architectural differences require checking if a combined compare-and-jump machine instruction exists. If the VADL specification does not specify such an instruction, the compiler generator has to generate a compiler that chains together the individual compare and jump machine instructions to ensure correctness. Section 3.13 describes the implementation algorithm in more detail.

**RQ2:** What is the semantic gap between instruction pattern selectors and instruction semantics?

We refer the reader to Section 2.4.2 for a definition of the *semantic gap*.

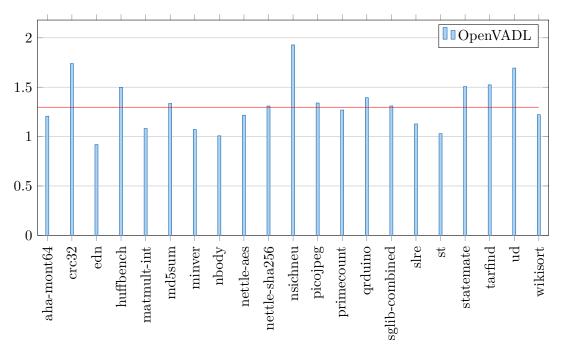

**RQ3:** What is the performance difference between VADL's clang and upstream

clang for RV32IM, RV64IM and AArch64?

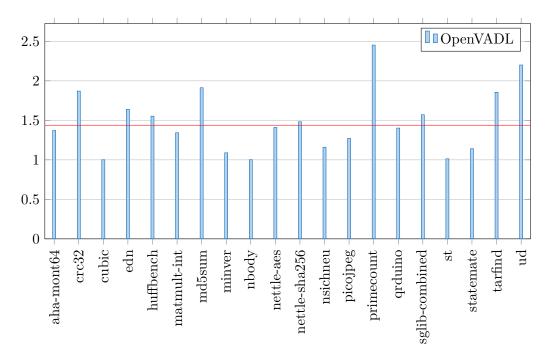

We evaluated RV32IM and RV64IM with the Embench suite Anob. For RV32IM, a program executed 29.73% more instructions than the clang upstream compiler on average for 21 of 22 benchmarks. For RV64IM, a program executed 43.83% more instructions than the clang upstream compiler on average for 20 of 22 benchmarks. All benchmarks were compiled with the highest optimization level -O3. We refer the reader to Section 5.1 for more details.

The generated AArch64 compiler does not support all the required functionality to run the Embench suite. We can compile and execute programs that use arithmetic, comparison and logical instructions. However, global variables, jump tables and indirect jumps are not supported yet. We refer the reader to Section [5.2] for more details.

### 3.2 Overview

The main contribution of this thesis is a compiler generator that automatically produces a compiler from a given VADL specification. OpenVADL is currently the only active implementation that supports VADL. OpenVADL reads the specification and transforms it into the VIAM, which is its IR. The project's architecture supports multiple generators, each producing an artifact that enables ASIP designers to perform DSE.

Figure 3.1 shows an overview of the compiler generator's architecture, which is split into two components. The GCB is responsible for the generic compiler generator functionality that is shared across multiple compilers and can be modularized. OpenVADL's distant goal is to generate multiple compilers, such as the GCC or a Java Just-In-Time (JIT) compiler. In contrast, the LCB's task is to generate a LLVM compiler.

The first task, in Figure 3.1 is the generation of encoding and predicate functions, which are described in Sections 3.3 and 3.4 respectively. Followed by the operand detection, which is described in Section 3.5. To conclude GCB's subgraph flow, the final step is the removal of branches that are edge cases, which is described in Section 3.6.1.

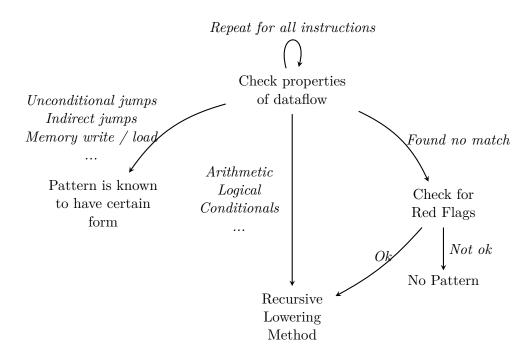

After these steps, the LCB analyzes the behavior of instructions, referred to as instruction classification. The classification algorithm assigns a classification label to each machine instruction. This label is used to generate instruction selection patterns, which are presented in Section 3.7.

Finally, the last step is to emit the rendered C++ and TableGen files. Each file has its own pass and is depicted as *File Emitter* in Figure 3.1. The generator's output is a set of files that overwrite an existing LLVM project. Afterwards, LLVM is compiled which results in an executable compiler called *clang*, which uses the VADL specification name as the target triple and acts as a cross-compiler for the specified

Figure 3.1: Compiler Generator Overview

VADL specification.

## 3.3 Encoding Generation

During the compilation, a compiler transforms a program into assembly or machine code. In VADL, each instruction has an assembly definition, shown in Listing 2.8, that is its human-readable representation. In contrast, the instruction's format defines the binary representation of the instruction, shown in Listing 2.7. As explained in Section 2.3.1, a field access function serves as a separation between instruction behavior and its decoding. However, a compiler encodes an immediate value into a format's field to emit machine code. The encoding function is the inverse function of the field access function.

To improve the readability of a specification, the compiler generator can automatically generate encoding functions in the following cases:

- 1. It is trivial to generate the encoding when the field access zero or sign extends a field. In that case, the encoding function truncates its operand to the field's bit width.

- 2. If the field access function shifts the value to the left, then the inverse function shifts the value to the right.

- 3. If the field access function uses addition or subtraction, then the inverse function is to invert the operations. The equations below show an example where f(x) is the field access function's value and x the encoded field value. The inverse function is the computation of x based on the field access function. The variable C is an arbitrary constant.

$$f(x) = x + C$$

$$\text{Let } y = f(x)$$

$$y = x + C$$

$$y - C = x$$

$$(3.1)$$

In the equation below the encoded value is negated and the left-hand-side has to be inverted.

$$f(x) = -x - C$$

$$\text{Let } y = f(x)$$

$$y = -x - C$$

$$y + C = -x$$

$$-y - C = x$$

$$(3.2)$$

When the compiler generator cannot generate encoding functions for more complex field access functions, encoding functions must be specified explicitly. Listing 2.9 shows an example where automatically generated encoding functions are manually added to the specification for the reader.

### 3.4 Predicate Generation

The field access function *immS* sign extends the field value, shown in Listing 2.7. Predicate functions are checked by the instruction selectors to verify that an immediate value's binary representation fits into the format's field. The predicate function is a boolean function that returns *true* when the immediate value fits, false otherwise. A machine instruction is selectable when all the used predicate functions are true. The term *used* refers to the fact that a format can have field access functions that are not used by any instruction.

As for the encoding generation, the compiler generator generates predicate functions automatically in the following cases:

- 1. It is trivial to generate the predicate when the field access zero or sign extends a field. In that case, the predicate checks whether the value fits into the underlying field.

- 2. If the field access function shifts the value to the left, then the lower bits must be zero, and the compiler generator adds a check to ensure the value is within the allowed range.

3. If the field access function uses addition or subtraction, then the predicate checks whether the value fits into the underlying field.

A predicate function must be provided in the specification when the mentioned cases do not apply. Listing 2.9 shows an example, where automatically generated predicate functions are manually added to the specification for the reader.

## 3.5 Operand Detection