# Instruction Set Simulation of VLIW Architectures in VADL

### DIPLOMARBEIT

zur Erlangung des akademischen Grades

### **Diplom-Ingenieur**

im Rahmen des Studiums

#### Software Engineering & Internet Computing

eingereicht von

#### Niklas Mischkulnig, Bsc.

Matrikelnummer 11809607

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Krall

Wien, 30. April 2025

Niklas Mischkulnig

Andreas Krall

# Instruction Set Simulation of VLIW Architectures in VADL

### **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

### **Diplom-Ingenieur**

in

#### Software Engineering & Internet Computing

by

**Niklas Mischkulnig, Bsc.** Registration Number 11809607

to the Faculty of Informatics

at the TU Wien

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Krall

Vienna, April 30, 2025

Niklas Mischkulnig

Andreas Krall

# Erklärung zur Verfassung der Arbeit

Niklas Mischkulnig, Bsc.

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Ich erkläre weiters, dass ich mich generativer KI-Tools lediglich als Hilfsmittel bedient habe und in der vorliegenden Arbeit mein gestalterischer Einfluss überwiegt. Im Anhang "Übersicht verwendeter Hilfsmittel" habe ich alle generativen KI-Tools gelistet, die verwendet wurden, und angegeben, wo und wie sie verwendet wurden. Für Textpassagen, die ohne substantielle Änderungen übernommen wurden, habe ich jeweils die von mir formulierten Eingaben (Prompts) und die verwendete IT-Anwendung mit ihrem Produktnamen und Versionsnummer/Datum angegeben.

Wien, 30. April 2025

Niklas Mischkulnig

# Kurzfassung

Von Hand ist das Entwickeln und Testen von neuartigen Prozessorarchitekturen ein zeitaufwendiger Prozess, da viele Instruktionen in vielen einzelnen Programmen implementiert werden müssen. Prozessorbeschreibungssprachen machen diese Arbeit sowohl weniger fehleranfällig als auch effektiver, sodass es möglich wird, sich einer guten Prozessorarchitektur schnell anzunähern. Die Vienna Architecture Description Language (VADL) ist eine solche Prozessorbeschreibungssprache. Very Large Instruction Words (VLIW) ist ein vor allem bei spezialisierten digitalen Signalprozessoren verwendetes Designmuster, bei dem mehrere Instruktionen in ein parallel ausgeführtes Paket zusammengefasst werden.

Bisher unterstützte VADL keine VLIW Architekturen, da es nicht möglich war, gültige Instruktionspakete zu beschreiben. Abgesehen davon war es außerdem nicht möglich zusätzliche (willkürliche) Bedingungen aufzulisten (beispielsweise um das gleichzeitige Schreiben auf ein einzelnes Register zu verhindern). Schließlich war VADL auch nicht in der Lage, einen funktionalen Simulator für VLIW Architekturen zu erzeugen.

In dieser Arbeit erweiterten wir die VADL Sprache, um gültige VLIW Pakete spezifizieren zu können: einerseits mit regulären Ausdrücken (mit zusätzlich Permutationen und Wiederholungen) und andererseits mit Bedingungen auf bestimmte Formatfelder von Instruktionen. Diese Information wurde dann verwendet, um in VADLs bestehendem funktionalen Simulator auch VLIW Instruktionen zu unterstützen. Zur Laufzeit wird das Programm gegen den regulären Ausdruck mithilfe eines deterministischen Zähler-Automaten ausgewertet, wodurch bei der Verwendung von Permutationen und Wiederholungen ein exponentiell großer Automat vermieden wird. Alle diese Funktionen wurden anhand von zwei VLIW Architekturen evaluiert (TI C6x und Qualcomm Hexagon), die (teilweise) in VADL spezifiziert und als Simulator getestet wurden.

### Abstract

Developing and prototyping novel processor architectures is a laborious task when done completely by hand, as there are many instructions to implement across many tools. Processor description languages make this work both less error prone and faster to iterate on, enabling rapid design space exploration. The Vienna Architecture Description Language (VADL) is such a language. Very Large Instruction Words (VLIW) is a design paradigm predominantly used by specialized digital signal processors, which groups instructions together into bundles which execute atomically in parallel.

Thus far, VADL hasn't supported VLIW architectures, as it was not possible to specify valid groupings of instruction types. Orthogonally to that, it also wasn't possible to have additional (arbitrary) constraints for these groups (for example to disallow concurrent writes to the same register). Furthermore, VADL's existing instruction set simulator generator also wasn't able to emit VLIW simulators.

In this work, we extended the VADL language to be able to specify valid VLIW bundles with a regular expression syntax (which additionally allows permutations and repetitions) and also arbitrary constraints to constrain specific fields of the instructions. This information was then leveraged to extend VADL's existing simulator capabilities to support VLIW architecture simulation. At runtime, the specified regular expression is matched against the instruction stream using a deterministic automaton with counters which prevents an exponential blowup when using permutations and repetitions. All added features were then evaluated by first specifying (parts of) the TI C6x and Qualcomm Hexagon architectures in VADL, and finally generating a simulator from the VADL Hexagon specification.

# Contents

| Κı       | urzfassung                                                                                               | vii       |  |  |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| Al       | Abstract                                                                                                 |           |  |  |  |  |  |  |  |

| Co       | ontents                                                                                                  | xi        |  |  |  |  |  |  |  |

| 1        | Introduction                                                                                             | 1         |  |  |  |  |  |  |  |

|          | 1.1 Motivation and Problem Statement                                                                     | 1         |  |  |  |  |  |  |  |

|          | 1.2 Research Questions                                                                                   | 2         |  |  |  |  |  |  |  |

|          | 1.3 Aim of this Work                                                                                     | 3         |  |  |  |  |  |  |  |

|          | 1.4 Structure of this Work                                                                               | 3         |  |  |  |  |  |  |  |

| <b>2</b> | Background                                                                                               | <b>5</b>  |  |  |  |  |  |  |  |

|          | 2.1 VADL                                                                                                 | 5         |  |  |  |  |  |  |  |

|          | 2.2 VLIW                                                                                                 | 8         |  |  |  |  |  |  |  |

| 3        | Related Work                                                                                             | 17        |  |  |  |  |  |  |  |

|          | 3.1 PDLs                                                                                                 | 17        |  |  |  |  |  |  |  |

|          | 3.2 VLIW Simulators                                                                                      | 18        |  |  |  |  |  |  |  |

|          | 3.3 Automatons                                                                                           | 19        |  |  |  |  |  |  |  |

| <b>4</b> | Implementation                                                                                           | <b>21</b> |  |  |  |  |  |  |  |

|          | 4.1 General Approach                                                                                     | 21        |  |  |  |  |  |  |  |

|          | 4.2 Language Design                                                                                      | 21        |  |  |  |  |  |  |  |

|          | 4.3 Decoding with Automatons                                                                             | 26        |  |  |  |  |  |  |  |

|          | 4.4 Constraints                                                                                          | 35        |  |  |  |  |  |  |  |

|          | 4.5 Simulation $\ldots$ | 35        |  |  |  |  |  |  |  |

| <b>5</b> | Evaluation                                                                                               | 39        |  |  |  |  |  |  |  |

|          | 5.1 Case Studies of Two Architectures                                                                    | 39        |  |  |  |  |  |  |  |

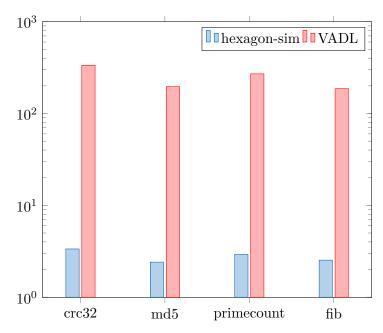

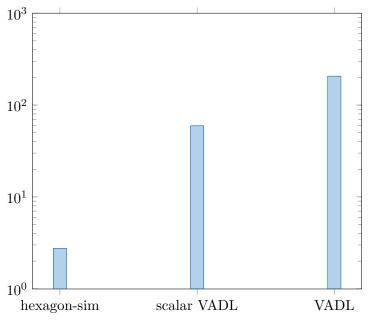

|          | 5.2 Simulator Performance                                                                                | 46        |  |  |  |  |  |  |  |

| 6        | Future Work                                                                                              | 49        |  |  |  |  |  |  |  |

| 7 Co   | onclusion                        | 51 |

|--------|----------------------------------|----|

| Overv  | view of Generative AI Tools Used | 53 |

| Biblic | ography                          | 55 |

# CHAPTER

## Introduction

#### 1.1 Motivation and Problem Statement

In the embedded computing landscape, it is essential to design processors with costs and performance characteristics which are viable for the specific application. This poses various challenges:

- multiple software artifacts are needed (such as compilers and simulators) to facilitate evaluation and design space exploration,

- specifying a complete architecture is very repetitive (there are many instructions that only differ slightly),

- resulting in very large projects (containing at least hundreds of instructions with dozens of variants each).

Specification languages specifically designed for this use case (domain specific languages, DSLs) offer a way to solve these problems: processor description languages (PDLs, or architecture description languages, ADLs) can be used in the design of new processor architectures to automatically generate the tooling (such as compilers, assemblers and simulators) required for testing and using these new architectures. They usually cover the instruction set architecture (ISA) and in some cases also the implementation of this instruction set in hardware (the micro-architecture, MiA). The Vienna Architecture Description Language (VADL) is such a PDL which covers both aspects.

PDL-based processor development is particularly useful for processors which are tailored to a specific use case in a specific project (application specific instruction set processor, ASIP). In these situations where various processor designs are evaluated for the specific application, automatically generating compilers and simulators (to compile and execute test or benchmark programs) speeds up the development cycle and the design space exploration.

#### 1. INTRODUCTION

Digital signal processors (DSPs) are a common processor type that is neither an ASIP nor a general purpose processor (as the ones used in most consumer devices). They are often used for fixed workloads, such as accelerating AI computations but also processing audio or RF signals, which require a high and consistent throughput and/or latency. Apart from having tailored instructions which are useful for matrix operations or Fourier transformations, many DSP processors are using a Very Large Instruction Word (VLIW) architecture. The more common superscalar architectures (used in modern consumer CPUs) determine which instructions can be executed in parallel at runtime in hardware. Conversely, VLIW is an approach where the compiler determines this ahead of time and groups instructions together into VLIW bundles (which contain multiple instructions that are executed in parallel). This can have a performance and resource consumption benefit for non-general-purpose computations.

Designing VLIW architectures in PDLs such as VADL is thus only possible if the language has a way of specifying which instructions can be grouped together into VLIW bundles. This information can then be used by the compiler to generate such bundles and by the simulators to execute programs.

Most VLIW architectures allow at most one instruction to use a given resource (such as functional units, each of which can perform one arithmetic operation or memory access) per cycle, requiring the ISA to specify how many such resources are available. Inside the VLIW bundle, these instructions can potentially have an arbitrary order, which cannot be specified with regular expressions alone (other than listing out all n! possibilities where n is the number of instructions per bundle). Often, there are also additional constraints which relate to the operands of the instructions themselves (e.g. a register can only be written to by at most one instruction per bundle).

#### 1.2 Research Questions

#### **RQ1:** How can VLIW bundles be described declaratively?

Our idea is to use regular expressions as an already well-known mechanism for declarative specifications, while extending them with additional syntax elements to more easily (and efficiently) describe repetition of elements and unordered permutations. Furthermore, constraints similar to first order logic should be able to constrain both the instruction type as well as the used registers and immediates.

**RQ2:** How can this grammar be represented as a parser which is efficient in regard to memory- and/or time-space?

All standard regular expressions can be transformed into a deterministic finite automaton. Our extension however will require this mechanism to be adapted to use an automaton with counters and constraints which can be turned into a deterministic automaton without exponential blowup.

**RQ3:** What is the performance overhead of accurately asserting valid VLIW bundles in a simulator?

Assuming a correct compilation pipeline, verifying in the simulator that all VLIW bundles are well-formed should not be necessary. However, especially during development of a novel ISA, this ensures that the assembler, compiler and linker are all behaving correctly. Furthermore, the hardware also performs this check (and can trigger an interrupt in such a situation).

#### 1.3 Aim of this Work

This thesis aims to extend the VADL system to support VLIW architectures.

- Support for VLIW architecture descriptions in VADL It should be possible to describe the most common existing VLIW ISAs using VADL. This specification should cover all details of the ISA, not only the sufficient grouping constraints but also all necessary constraints, as the description is also intended to eventually allow compiler backend generation.

- Support for VLIW architectures in the VADL simulator To accompany the previous goal, these specifications can also be used to generate an instruction set simulator which is able to decode and execute programs of VLIW architectures. The simulator should also ensure the correctness of the executed program, just like the hardware also detects invalid bundles.

#### 1.4 Structure of this Work

Chapter 2 starts by giving an introduction into the VADL language and into the basic concepts of VLIW architectures including three concrete VLIW ISAs that will be used as a running example throughout this work. Chapter 3 presents an overview of the existing work covering processor description languages, VLIW simulators, and automatons. In chapter 4, we describe the approach taken and implementation performed to support VLIW in the VADL language and simulator. Chapter 5 evaluates our changes by specifying some VLIW architectures in the VADL language, and by measuring how the VADL simulator performed compared to existing tools. Finally, chapter 7 concludes this thesis.

# CHAPTER 2

# Background

This chapter describes the most important aspects of the VADL language (excluding the VLIW support that was introduced in this work and will be described later on), and the fundamentals of VLIW architecture to be able to understand which problems need to be addressed to support VLIW in VADL.

#### 2.1 VADL

VADL is a language to describe processor architectures. It always contains the instruction set architecture which is the processor behavior that users/developers can depend upon (also regarding backwards and forwards compatibility). Additionally, the micro architecture as the (internal) implementation of an ISA can be specified as well. An important design decision was to clearly separate ISA and MiA, both to differentiate the two aspects and also to make it easy to experiment with different MiAs which implement the same ISA during the design phase.

There are multiple backends for the VADL compiler that can generate different artifacts: simulators (both functional and cycle-accurate), a compiler (including assembler and linker), and hardware (Chisel code that can be compiled to Verilog and eventually etched into a silicon chip). This has guided the language design to make it even feasible to generate a compiler (which requires knowledge about the structure of the ISA and the behavior of the instructions to derive the necessary information for instruction selection), or the hardware (which is inherently parallel instead of sequential as most programming languages are).

For this reason, the VADL language itself has a functional style, apart from writes to registers or the memory. These writes are also not visible until after the current instruction has finished executing, which aligns with the parallel execution paradigm of the hardware. An ISA is declared with **instruction set architecture** which then contains all structural elements and instructions, as shown in Listing 2.1.

There are some resources that model the state of the processor, most importantly registers and the main memory. Listing 2.1 shows an example of an ISA called DSP with a byte-addressable 32-bit main memory, 32 general purpose 32-bit registers and a separate 4-bit register for predicates. The other basic datatypes apart from Bits are UInt and SInt which are all arbitrary length bit vectors and integers, respectively. All of these types have the concrete bit width as a type parameter, but type inference allows also using the abstract type when casting values.

The most important register is the program counter. It can have a next annotation to denote that it points to the next instruction, as opposed to the instruction that is currently being executed (which is the default behavior). This is a somewhat arbitrary decision from an ISA perspective that is nevertheless required for some ISAs (and is usually done to simplify the microarchitecture implementation).

```

1 instruction set architecture DSP = {

memory MEM : Bits<32> -> Bits<8>

2

register file X : Bits<5> -> Bits<32>

3

register PRED: Bits<4>

4

5

6

[next]

7

program counter PC : Bits<32>

8

9

// ...

10 }

```

Listing 2.1: VADL Resource Declarations: Registers and Memory

Each instruction is composed of multiple aspects: the behavior and the encoding (both immediates like operands and the opcode). As shown in Listing 2.2, there's the instruction format which has a base type (32 bits) and assigns names to some bit ranges (similar to C's packed bit fields). These format variables can then be used in the **encoding** block to specify one or multiple opcode fields. Format variables can also be referenced in the **instruction** body itself, like in the ADD instruction which adds the immediate in rs2 to the register with index rs1 and stores the result in register rd.

Most instructions don't modify the program counter, in which case the program counter is implicitly incremented to point to the next instruction (based on the length of the current instruction).

The instruction CCALL in Listing 2.2 shows how a common RISC conditional call instruction might be implemented by setting X(31) (the link register) to the return address and incrementing the program counter by a shifted displacement constructed from format variables. It demonstrates basic control flow (based on the predicate register from above) and special methods available for the program counter: PC.current refers to the address of the current instruction and PC.next refers to the address of the following instruction (assuming no jumps). For most architectures, these are just syntactic sugar (i.e. a constant offset) since the length of the current instruction is always known (the format of CCALL is F whose size is Bits<32>). However, this will become more complex with VLIW instructions.

```

instruction set architecture DSP = {

2

// ...

3

format F : Bits<32> =

4

5

{ par

[31]

6

, rs2

[20..16]

7

rs1

[15..11]

[10..6]

8

, rd

opcode [5..0]

9

10

ş

11

instruction ADD : F =

Ł

13

X(rd) := X(rs1) + rs2

14

}

15

encoding ADD = { opcode = 0b00'01'00 }

16

17

instruction CCALL : F =

18

19

Ł

if PRED != 0 then {

20

X(31) := PC.next

21

PC := PC.current + ((rs2, rs1, rd) << 2)

22

ş

23

24

Ş

encoding CCALL = { opcode = 0b00'11'00 }

25

26 }

```

Listing 2.2: VADL Instruction Declarations

For VLIW, it will prove useful to be able to group instructions into sets, which in VADL are called **operation** (these are also used in the microarchitecture specification). They can be declared with annotations or by listing out the instructions (or other operations for a set union) in the declaration, as shown in Listing 2.3. By themselves, operations have no inherent semantics and only exist to be able to easily refer to multiple instructions in other parts of the language.

```

1 instruction set architecture DSP = {

2  // ...

3

4  [ operation OP_ALU ]

5  instruction SUB : F = // ...

6

7  operation OP_ALU = { ADD }

```

```

8 operation OP_MEMOP = { }

9 operation OP_ALU_MEMOP = { OP_ALU, OP_MEMOP }

10 }

```

Listing 2.3: VADL Operations

VADL also supports many more language constructs that are not relevant to this work, such as syntactical macros, microarchitecture/pipeline specification, and exceptions. See [Fre+25] for a full description of the language.

Finally for simulator or hardware generation, a **micro processor** declaration is required, which provides initial values for registers and the memory, and specifies a stop condition (which is essential for a simulator to cleanly exit, but does not apply to the compiler or the hardware backend). Listing 2.4 shows a **micro processor** declaration for the DSP ISA that was described thus far. It sets an initial value for the program counter and exits automatically once the program counter has a specific value. Upon startup, the stack pointer is initialized (and if there were any, control register initialization would also be done here).

```

1 instruction set architecture DSP = { /* ... */ }

2 micro processor CPU implements DSP = {

start = 0 \times 80000000

3

stop = (PC = 0xeeee'eeee)

4

5

startup -> ( ok : Bool ) =

6

7

Ł

X(29) := 0 \times 40000000

8

PC := start

9

10

11

ok := true

}

12

13 }

```

Listing 2.4: VADL Microprocessor Declaration

#### 2.2 VLIW

VLIW (Very Large Instruction Words) is, at its core, an "architectural design philosophy" ([FFY05, p. 54]). It was developed to increase processor performance (which can be expressed in the number of instructions executed per clock cycle, IPC), just like today's ubiquitous superscalar processors, by leveraging instruction level parallelism (ILP).

The following three sections about VLIW's core principles are based on [FFY05, Chapter 3].

#### 2.2.1 Motivation

**Pipelining** ILP is crucial to execute one or even more instructions per clock cycle. Executing an instruction fully in a single clock cycle is not possible, so all processors are *pipelined*, meaning that the instruction execution is split up into multiple stages (such as fetch, decode, execute, memory operations, result write-back). In some situations, this allows the instructions to be executed in an overlapping fashion, achieving an IPC of one (though in reality, five stages of five different instructions are executed every cycle). However, once an instruction depends on the result of a preceding instruction that is also still executing, it has to be *stalled* and wait until the result is available. This is called a *data hazard*, caused by the data dependency between the instructions. Similarly, conditional jump instructions also cause *(control) hazards* because their execution result determines which instruction to run next.

**Superscalar** Superscalar architectures (also called *multiple-issue* architectures) are able to achieve an IPC greater than 1 by issuing (starting execution of) more than one instruction at once. Compared to pipelining by itself, this requires that the processor is able to execute a single stage of multiple instructions per cycle, thus its functional hardware units (like an ALU for arithmetic operations) need to be duplicated multiple times. Hazards prevent leveraging superscalarity just like they do for pipelining itself, but the relative slowdown is even higher, because a theoretical IPC of (e.g) 2 falls to below 1.

Processors based on the concepts introduced thus far would work somewhat well, but the data and control hazards would pose a bottleneck for performance.

**OoO and Speculation** Therefore, essentially all modern superscalar processors (for high performance, so excluding for example low-power embedded applications) perform *out-of-order (OoO) execution*, which handles data hazards by executing instructions still further ahead in the instruction stream that don't have to wait for a result of a preceding instruction. Control hazards are handled using *speculative execution*, by guessing the result of conditional jumps and then rolling back all changes in case the jump was predicted incorrectly. For this, the processor has to analyze the data dependencies between instructions at runtime to determine how to reorder and where to speculate.

Another perspective onto this approach is that the program (instruction stream) doesn't specify the execution order anymore, but is only a serialization of a graph that represents the computation that should be performed. OoO execution reorders it into an equivalent serialization, while speculation handles the side effects that are necessarily part of the not completely side-effect-free computational graph (notably the jumps, memory writes, and architectural register writes).

**VLIW** An alternative solution for superscalarity that works without OoO and speculation is to explicitly group instructions without any dependencies together. This way the processor can simply execute one grouping after another without any dependence

#### 2. Background

analysis while still issuing as many instructions as possible. The dynamic dependence analysis and scheduling is now moved from the processor hardware into software, where the compiler generates a static schedule.

For non-VLIW architectures, the number of functional units is part of the microarchitecture and is thus not exposed in the ISA. In a VLIW processor, this becomes part of the ISA as compilers need to know which units are available when grouping instructions together. Similarly, register bypassing is usually a microarchitectural detail, but some VLIW architectures expose it in the ISA by allowing reading some values which were only computed in the same group.

The benefits of VLIW are that fast processors are less complex (because the static scheduling happens ahead of time, requiring less run time resources) and thus cheaper to produce. For certain workloads, they can be faster overall. On the downside, exposing more microarchitecture in the ISA leads to worse backwards and general compatibility of binaries across processors (both across versions of the same MiA and across different processors with the same ISA). An important aspect to consider is that the way scheduling/grouping is done by the compiler affects VLIW performance much more, as bad scheduling and subsequently many very short groups effectively turn a VLIW processor into a much slower non-superscalar processor.

This shows why VLIW processors are currently only used in embedded applications: lower cost, firmware that doesn't need to be compatible with other devices, DSP use-cases that tend to perform well in VLIW architectures.

#### 2.2.2 Terminology

There are no standard terms used in literature and by processor designers for the *in-struction unit* (e.g. a single ADD instruction) and the resulting *group* of instruction units (e.g. two parallel ADD instructions), as the term *instruction* is now ambiguous.

There are two different dimensions to differentiate: the abstract entities in general, and the encoding (which is some bit vector) of these entities.

The abstract *instruction group* (not a meaningful concept in non-VLIW architectures) is called *(issue) group*, *bundle* or *(execute) packet*. The abstract *instruction unit* (what non-VLIW architectures call *instruction*) is sometimes called operation or simply instruction.

An encoded instruction group is sometimes referred to as a *word* or *fetch packet*. An encoded instruction unit as a part of the bundle word might be referred to as a *syllable*. [FFY05, p. 87]

For example, Qualcomm uses *instructions* and *packets* for their Hexagon architecture [Mana]. Texas Instrument's C6x processor series has *instructions* in *fetch/execute packets* [Manc]. Intel Itanium uses the terms *instructions* and *instruction group* (and additionally *bundle* for the subgroup described below in 2.2.3) [Manb].

In this thesis, we use *instruction* for the atomic instruction unit, the remaining terms are unambiguous anyway.

#### 2.2.3 Encoding Schemes

There are multiple high-level approaches to encode a group of instructions into a bit vector:

**Fixed-Width** An *n*-issue processor needs at most *n* instruction in the group. The most straight-forward encoding is a group word which always contains *n* instructions, with each slot being assigned to a fixed functional unit. This is also the easiest encoding to decode (because of the fixed instruction-to-unit mapping). The major downside, however, is that many groups end up containing many no-op instructions to pad out the unused functional units. This leads to wasted memory and also (if employed) more instruction cache misses and thus higher energy consumption. [FFY05, p. 114]

| ADD | ADD | NOP | LOAD | NOP | ADD | SUB |  |

|-----|-----|-----|------|-----|-----|-----|--|

|-----|-----|-----|------|-----|-----|-----|--|

Figure 2.1: An example for a fixed-width encoding scheme, each group contains five instructions.

Therefore, the following encoding schemes all rely on variable length group words (to prevent excessive no-ops).

**Fixed-Overhead/Mask** Each word starts with a syllable-sized mask that specifies both the size of the group and the mapping of instruction to functional unit. This way, the decoder can effectively expand the compressed word into the equivalent fixed-width encoding. As the name implies, short words have a proportionally larger overhead. [FFY05, p. 115]

| 0 | $\downarrow \\ length = 2 \\ units: ALU2, LD$ |  |  |  |  |  |

|---|-----------------------------------------------|--|--|--|--|--|

Figure 2.2: An example for a mask-based encoding scheme: two groups with different lengths and what information is encoded in the mask.

Variable-Overhead/Distributed The fixed overhead can be distributed into the syllables themselves: using a start/stop/parallel bit per syllable that specifies whether the start/end of the current bundle was reached (thus encoding the length), and also encoding the appropriate unit in the syllable directly. This approach is used in the TI C6X and Qualcomm Hexagon architecture. [FFY05, pp. 115 sq.]

#### 2. Background

| 1 | ADD | 1 | ADD | 0 | LOAD | 1 | ADD | 0 | SUB |  |

|---|-----|---|-----|---|------|---|-----|---|-----|--|

|---|-----|---|-----|---|------|---|-----|---|-----|--|

**Figure 2.3:** An example for a distributed encoding scheme, a preceding parallel bit indicates if a given instruction is the last instruction in the current group. The function unit is also encoded as part of the instruction (even if this isn't shown in the figure).

**Template** By encoding the group ending and the unit mapping into a group header, the encoding can be made more flexible: now, multiple subgroups that each have a header can be chained to build the group itself. *Stops* can be at arbitrary positions inside (or at the end of) the subgroups, depending on the chosen template bit encoding. One shortcoming is that this template header doesn't allow all possible combinations of instructions and stops/chaining, so sometimes no-ops still need to be inserted. Intel Itanium uses this encoding. [FFY05, pp. 116 sq.]

| template  | ADD      | ADD     | LOAD | template | SUB | LOAD | AND |  |

|-----------|----------|---------|------|----------|-----|------|-----|--|

| +         |          |         |      | ¥        |     |      |     |  |

| units: AI | LU1, ALU | J2, LD1 |      | units: A |     |      |     |  |

| parallel  |          |         |      | stop aft |     |      |     |  |

Figure 2.4: An example for a template-based encoding scheme: the two fixed-length subgroups (each with their own functional unit mapping) encode a group of five instructions and another instruction that will be executed as part of the next group.

#### 2.2.4 Examples

After these theoretical foundations, the following (mostly) contemporary VLIW architectures aim to illustrate some ISA features that are unusual compared to the more well-known regular superscalar architectures.

#### Texas Instruments C6000/C6x

The Texas Instruments TMS320C64x architecture [Mana] (with alternative names C6000 series or just C6x) is a 32-bit DSP architecture targeted at telecommunications and other signal processing applications.

The functional units are split into two subsections (called data paths) in the processor, each containing the same four functional units (multiplication, logical operations, logical operations or branches, memory accesses). Each data path has its own register file with 32 registers, while still allowing one source register read of the opposite register file per cycle via a *cross path*. Because of the separate register files, two functional units of the same type cannot be used interchangeably as they each have access to different registers and thus the unit assignment is part of the instruction encoding.

The architecture has exposed all instruction latencies in the ISA, meaning there are delay slots not only for branches but other instructions as well. Stores and many simple instructions execute in a single cycle without a delay slot, some instructions such as DOTP2 (a signed dot product of two packed 16-bit vectors stored in two registers) have three delay slots before the result is written back, loads have four delay slots, and branches have five delay slots. Nevertheless, the functional unit latency is always one cycle, meaning that all instructions can be dispatched continuously on every cycle, just the result is only available with a delay. Due to the explicit delay slots, the MiA doesn't have to handle any hazards and doesn't have to stall the pipeline.

There are *fetch packets* and *execute packets*. Fetch packets are always 256 bits long (eight regular instruction words) and execute packets (containing up to eight instructions) are some subsequence of instructions in the fetch packet (but can still span across two fetch packets) that execute in parallel.

Regular execute packets can contain up to eight instructions in any order (to fill the two data paths with up to four instructions each corresponding to the functional units). They are encoded with a distributed encoding with parallel bits (as shown in figure 2.3).

The C64x+ ISA also supports *compact instructions* which use a template-based encoding that can use shorter 16-bit instruction words for higher code density. In that case, the eighth instruction in the fetch packet is a header specifying which instructions in this packet are encoded in the compact format, where the parallel stop bits inside the packet are, and some other modifiers. Naturally, only a subset of the instructions and operands can be encoded in the 16-bit compact format.

#### Qualcomm Hexagon

Qualcomm Hexagon [Cod+14; Mana] is a 32-bit DSP architecture used in coprocessors of Qualcomm mobile CPUs for modern and multimedia acceleration. It is a more modern architecture without delay slots and with simultaneous multithreading.

Instructions are partitioned into ten instruction classes, each bundle can then contain up to four instructions that are scheduled into one of four slots, each of which can execute a subset of instruction classes. For example, LD (load) and ST (store) instructions can execute in slot 0 and 1, while JR (jump with register) instructions can execute only in slot 2. The order of instructions in a bundle matters (in reverse order corresponding to the slots) and in case a bundle contains fewer than four instructions, a no-op is implicitly inserted for the slot that remains empty. The bundles use a distributed encoding with parallel bits.

Hexagon's approach for a compressed encoding are *duplex instructions*, which are pairs of instructions that are encoded as a single 32-bit word. A bundle can contain at most one duplex instruction, which must also be the last instruction in the bundle. As always, only a specific subset of instructions, combinations and operands are allowed as duplex instructions.

There are *constant extenders* which are encoded as a 32-bit prefix to enable instructions with full 32-bit immediates (26 bits in the extender plus 6 bits in the instruction itself)

for a subset of instructions, which makes the ISA effectively variable length. Bundles can, however, still only contain four words, so for example either four instructions or three instructions with one constant extender.

The two parallel bits in each instruction are also used for hardware loop support to mark the start and end of the loop body. The loop is then executed for a specified number of iterations without having to include any compare or branch instructions at the end of the loop body (see listing 2.5).

1 loop0(start,#3)

2 start:

3 { R0 = mpyi(R0,R0) } :endloop0

**Listing 2.5:** Hexagon Hardware Loop Example which executes a multiplication three times without any compare or branch instructions.

There are multiple types of instructions that seemingly defy the usual VLIW approach of executing all instructions in parallel (with results only being available in the next cycle).

*Dual stores* occur when a bundle contains two memory store instructions, these are then defined to be executed sequentially. Similarly, *dual jumps* occur when a bundle contains two jump instructions, which allows constructs such as **if** ... jump X **else** jump Y or **if** ... jump X **else if** ... jump Y.

The other type of sequential execution (or rather result forwarding exposed in the ISA) are *new-value* and *dot-new* operations (which use a .new operand suffix in the assembly): *new-value stores* allow storing a value that was computed in the same bundle (and therefore same cycle), while *new-value compare jumps* allow conditional jumps depending on a value that was computed in the same bundle. Listing 2.6 contains an example for both of these instructions. Only these two specific types of instructions support new-value operands. Listing 2.6 also shows how predicate registers can be written and read in the same cycle.

```

1 {

2

R0 = R4 + \#8

memw(R5) = R0.new

3

4 }

5 {

R0 = memw(R4 + \#8)

6

if (cmp.eq(R0.new,#0)) jump:nt target

7

8 }

9 {

P0 = cmp.eq(R2, #4)

10

if (P0.new) R3 = memw(R4)

11

12

if (!P0.new) R5 = #5

13 }

```

14

Listing 2.6: Hexagon example of new-value operations for storing a newly computed value, branching based on a newly computed value, and using a newly computed predicate.

Finally, multiple compare instructions writing to the same predicate register in a single cycle automatically AND the results together, as shown in listing 2.7.

```

1 {

2     P0 = cmp.eq(R0, #2)

3     P0 = cmp.eq(R1, #7)

4     if (P0.new) jump:t target

5 }

```

**Listing 2.7:** Hexagon example for new-Value predicates and auto-AND predicates that performs a jump if two equality checks evaluate to true.

#### Intel Itanium

Intel's Itanium architecture (IA-64), was developed as the 64-bit RISC successor to Intel's X86/IA-32 CISC architecture. It was the result of a partnership with HP (and their Explicitly Parallel Instruction Computing *EPIC* architecture) [Lei19].

It uses a template based encoding as shown in figure 2.4. A 128-bit bundle contains three 41-bit instructions and a 5-bit template. The realized microarchitectures only ever supported executing two bundles (six instructions) in parallel, but this approach would have allowed more powerful processors with more parallelism in the future (without having to recompile any code). The 5-bit template can contain one of 24 different combinations of slot-to-unit assignments and stop positions (plus eight reserved values). Two of the templates can contain an extended instruction, which consists of a 32-bit instruction with a 32-bit suffix to achieve a long immediate integer or branch target.

There are 128 64-bit registers, of which 96 are *stack registers*. They are stored and restored transparently onto or from main memory when performing procedure calls when running out of registers. This is used instead of the more common (e.g. with x86/ARM) approach of always explicitly saving registers onto a stack in memory.

As opposed to the other architectures, Itanium also has a focus on speculation in addition to the VLIW-based ILP. There are *advanced load* instructions which are similar to load-reserved instructions (but without multithreading) which load a value in advance and then potentially re-execute code that depended on the value in case it was outdated. [Manb][Dan, pp. 97-120]

Unlike C6x and Hexagon, the Itanium architecture was discontinued by Intel and the last processors were shipped in 2021 [Arsa]. Even before that, Microsoft decided to stop supporting Itanium in future versions of their server software in 2010 [Arsb]. One of the

#### 2. Background

reasons for this failure was that the Itanium compiler did not produce good enough code to take advantage of the architecture with its VLIW and speculation aspects. As opposed to fixed-workload DSP applications, general purpose workloads made unpredictable and variable latency branches and memory accesses hard to schedule while still keeping the VLIW pipeline filled. As a competing architecture, AMD's 64-bit x86 efforts had more backwards-compatibility and multithreaded processors lead to more performance gains without the technical complications of Itanium. [Lei19]

# CHAPTER 3

# **Related Work**

#### 3.1 PDLs

ISDL [HHD00] is a PDL specifically designed for VLIW architectures. Like VADL, it also supports automatically generating an assembler, instruction set simulator, and code generator. VLIW bundle constraints are described using a language for temporal logic predicates, thus being more expressive than VADL's regular expression approach. The simulator performs static binary translation ahead-of-time, meaning the decode speed does not influence the simulator's performance.

ISADL [XL23] focuses on automatically generating an instruction encoding based on requirements (number of functional units, list of encoding fields included in all instructions, list of encoding fields used by some subset of instructions), with the goal of generating an optimal instruction encoding (regarding binary size) for VLIW architectures. Instruction semantics or constraints are not covered by the language itself.

TDL [Käs03] is not specifically a PDL, but designed for generating optimizers to run on some compiler output. The specification is split into three sections: resources such as registers and memory (and notably, also functional units, unlike in VADL), instructions, and constraints. It allows specifying VLIW constraints in a very similar way as VADL (see section 4.2), using boolean expressions with some special operators to check for membership of an instruction in an operation set.

In nML [FVF95], instructions are described using hierarchical top-down composition of alternatives parts (OR) or parallel parts (AND). In this model, VLIW bundles themselves could be described as instructions without the need to separately specify constraints. Arbitrary additional constraints that go beyond functional unit availability can, however, not be modeled like this.

LISA [Pee+99] is a PDL designed to be able to generate cycle-accurate models of DSP architectures (specifically the TI C6x architecture). LISA is similar to VADL in that

#### 3. Related Work

there are resource definitions for registers and memories, and then each instruction has an assembly encoding, binary encoding and behavior. The root instruction is declared explicitly using an unnamed instruction which can contain one or more sub-instructions, with the same syntax used for declaring the source and destination registers of instructions. The same mechanism can also be used to declare a (pseudo) instruction representing some set of instructions.

[Bra+04] presents an extension of LISA for replacing its C-based behavior definition with more restricted assignments, that also allows composing operations together (analogous to bundles). Multiple VLIW architectures were modeled with this language, but the paper doesn't describe how constraints were handled.

[Res+03] presents a retargetable simulator which has *instructions* (bundles) with *slots* for *operations* (instructions) and also *operation classes* to group instructions. While VLIW architectures are listed as target architecture for this simulator generator, no such architectures were used in the evaluation (neither regarding performance nor expressiveness).

[P+11] describes an extension of the ISAC language (which itself is based on LISA) for VLIW architectures and multi-core processors. Bundle decoding and encoding is specified with a manual implementation using a subset of C, making it harder to automatically generate optimal decode trees for both the simulator and a hardware implementation (using VHDL). The paper mentions that there are predefined bundle compression types (e.g. distributed or template-based encoding) and a way to succinctly define multiple clusters (data paths), but doesn't go into detail how these are specified in the language.

Hewlett-Packard's PICO system not only generates an assembler, compiler, simulator and hardware implementation of a described VLIW processor, but also automatically finds the most cost-effective implementation of a system composed of the VLIW processor, a co-processor used for acceleration, and a cache subsystem. It modeled constraints as exclusion groups (whose contents cannot be executed in parallel, similar to functional units), which can contain both instructions and other instruction groups. The system is based on templated encoding (which was developed for HP's EPIC architecture which turned into Intel Itanium) [ARRK99] [ARR00]. [AMR00] used the PICO system for design-space exploration to demonstrate how adding more templates can reduce code size.

#### 3.2 VLIW Simulators

[HPF13] uses static binary translation (with manually implemented ISA frontends) to simulate the TI C6x architecture by leveraging the Linux kernel's KVM interface for acceleration. The research group's earlier paper [MFP12] describes how register allocation was used to simulate parallel execution by employing register renaming and how delay slots were translated. [BBR00] describes a simulator which performs, among other things, TI C6x decoding and also pipeline simulation using a reservation table. Parallel execution semantics are modelled by reading from one register files while writing to another separate register file, so that writes within the same bundle aren't visible until the next machine cycle.

[ZHS10] implements an instruction set simulator for TI C6x using queues, which trigger the individual pipeline stages after the correct number of machine cycles (the latency) has passed. Parallel execution semantics are observed as the write back stage is only executed once all operands are already read.

[WYW08] is a simulation framework for VLIW architecture evaluation (consisting of an assembler and simulator), the paper doesn't describe how the VLIW architecture itself is described or parameterized. The simulator has two different execution modes: a purely functional instruction set simulator, and a cycle-approximate simulator emulating the microarchitecture.

[RGD06] introduced using colored petri nets for cycle-accurate VLIW simulation by modelling the execution pipeline as a petri net with individual tokens (instructions) progressively moving through the stages. [Yan+16] leverages colored petri nets for implementing a cycle-approximate VLIW simulator on top of the gem5 simulator.

[Mor+97] describes a framework developed by IBM and consisting of a VLIW compiler and binary translator (outputting PowerPC binaries), which can also include instrumentation for cycle counting. It was designed for the ForestaPC architecture, which has tree instructions instead of regular VLIW bundles. Like bundles, all operations in a tree instruction are also executed in parallel, but the tree can have conditional branches allowing predicated execution.

Tree instructions can be decomposed at runtime depending on the processor's execution width. This approach can have less than a 10% runtime performance overhead compared to compiling for a specific VLIW width while still allowing a single binary to be used with different VLIW microarchitectures [MM97].

[Liu+05] also uses tree instructions but includes differential encoding which is able to more efficiently compress instructions by referencing back to an encoded instruction and re-instantiating it with different operands. Across multiple benchmarks, this reduced the program size by around 64%.

#### 3.3 Automatons

The most well known deterministic finite automaton (DFA) construction method is Thompson's construction [Tho68] (which recursively builds an automaton composed of small building blocks) followed by determinization using powerset construction [RS59] (which simulates all reachable combinations of non-deterministic states).

Glushkov's construction algorithm [Glu61] creates an  $\varepsilon$ -transition-free non-deterministic finite automaton (NFA). Each symbol in the regular expression becomes a state, and

#### 3. Related Work

the transitions are then defined using the symbol's first, next and last sets (similar to the ones in parser theory)

Brozozowski [Brz64] introduced *derivatives* of regular expressions (a  $u^{-1}L$  which gives all words in the language L starting with the string u with prefix u removed). This notion can then be used to directly generate DFAs from regular expressions. Based on Brozozowski's derivates, Antimirov [Ant96] used a similar approach called *partial derivates* to instead generate NFAs from regular expressions.

Another method that will be used later in this work are *pointed regular expressions* [ACT10] which can be used to directly generate DFAs. Section 4.3.2 will describe this approach in more detail.

A common extension of the normal regular expressions use *permutations* or *unordered* concatenation (being able to specify that multiple symbols have to be matched, but in any order), and repetition or numerical constraints (being able to specify that a symbol has to matched at least n but at most m times). This class of regular expressions are generally exponentially more concise while still describing the same language as normal regular expressions [Hov12]. However, regular expressions with permutations already make the membership problem NP-hard (that is, even without repetitions) [Hov12].

Some schema languages such as SGML and XML use a different set of regular expressions, supporting both more features (permutation and repetition) while only allowing a subset of the usual regular expressions (*1-unambiguous languages*, meaning that all words can be matched in only one way by the regular expression, and with only an one-symbol lookahead) [BKW98].

[Hov09] developed a method to construct DFAs with counters for regular expressions with repetition. It only works for a subclass of regular expressions (*counter-1-unambiguous* expressions which follow the exact same reasoning as the 1-unambiguity from above, only extended for this superclass of counter automatons) but constructs a DFA in polynomial time while also being able to determine in polynomial time whether the regular expression input is within the supported subclass.

[BC08] also uses counters to support repetitions and back-references. It acknowledges that the number of active counters needed during matching is not constant (which is an alternative solution to restricting the algorithm to counter unambiguous languages only), instead allocating more counters as necessary.

[Tur+20] also generates counter-automatons from regular expressions with repetition, first by constructing a nondeterministic automaton based on Antimirov's partial derivates, and then determinizing them in a second step. Only a subset of regular expressions can be accurately represented because this approach can result in an over-approximation of the original regular expression (i.e. the automaton matches a word that is not matched by the regular expression, so called *non-uniformity*, which is once again related to the problem of counter ambiguity).

# CHAPTER 4

# Implementation

This chapter discusses the main contributions of this work. Section 4.1 and section 4.2 describe how VLIW support was added to the existing VADL language for non-VLIW architectures (as described in section 2.1). Section 4.3 presents how group expressions are turned into an automaton. Finally, section 4.4 outlines the constraint implementation and section 4.5 describes how correct bundle execution semantics are ensured.

#### 4.1 General Approach

One core goal of VADL is to support generating multiple artifacts, such as simulators and compilers, from the same specification. This necessitates a declarative specification that is also high-level enough to not be too specific to a single artifact.

VADL already supports regular (superscalar) instructions and instruction sets. These constructs should be reused for the instructions in the VLIW groups by composing them into groups by specifying which sequences of instructions are valid.

We chose to start with adding support for fixed-width and distributed encodings, which are used by the Hexagon and C6x architectures.

#### 4.2 Language Design

There are two independent fundamental aspects influencing whether a given group is valid: functional unit availability (e.g. number of ALUs, number of memory ports), and preventing parallel writes. Additionally, the instructions might also have to be in a specific order (e.g. first ALU operations, then followed by memory operations), which can simplify the decoder implementation. (There might be more constraints imposed by an ISA which don't fit into one of these two aspects, usually because constraints imposed

#### 4. Implementation

by the MiA have to become part of the ISA, which includes arbitrary design decisions made to improve performance or lower production costs).

Functional unit availability and order are described in VADL with an extended version of regular expressions. Data dependencies and all other constraints which cannot (easily) be expressed in the regular expressions are described in logical constraints using a version of first-order logic. This is also how the stop/parallel bits of the distributed encoding are specified.

#### **Regular Expressions**

The extended regular expressions are specified in a **group** definition (as shown in listing 4.1). Any **instruction set** may contain at most one **group** definition. The name of the definition is irrelevant for the regular expression, but will be used in the constraints (see below).

As opposed to normal regular expressions which operate on strings of characters, these operate on instructions and operations (which are sets of instructions). At runtime, a sequence of instructions is matched against the regular expression to determine if it is a valid group. Instructions are, however, not used in the regular expression syntax: instead operations are the terminals in the syntax. They have the semantics of matching any instruction that is contained in the operation.

The syntax itself (specified in listing 4.2) is very similar to standard regular expressions: there are the operation *literals*, *alternatives* (expressions separated by a vertical bar) and *sequences* (expressions separated by a dot). The extensions are *repetitions* of literals by specifying a range in angle brackets after a literal (such as A<2..4>, which means "at least 2 and at most 4 repetitions of any instruction contained in operation A"), the lower end of the range can also be 0. The other extension are *permutations* that use curly brackets, which match all listed subexpressions but in any order.

Listing 4.1 shows some examples of group definitions (which are all possible but not necessarily practical as real-world VLIW encodings).

```

1 instruction set architecture DSP = {

// ...

2

3

operation A = {ADD, SUB}

4

operation LD = {LOAD, STORE}

5

operation J = {JUMP, JUMP_COND}

6

7

group VLIW = (A.LD)

// A followed by LD, meaning

8

// (ADD or SUB) followed by (LOAD or STORE)

9

group VLIW = (J | A | LD) // J or A or LD

11

// (A followed by LD) or (LD followed by A)

12

group VLIW = {A, LD}

13

// 0-2 As followed by optional LD followed by optional J

14

```

22

```

15 group VLIW = ( A<0..2>.LD<0..1>.J<0..1> )

16 // as previous group, but any order

17 group VLIW = {A<0..2>, LD<0..1>, J<0..1>}

18

19 group VLIW = ( {A<0..4>, LD<0..2>} . J . (A|LD) )

20 }

```

Listing 4.1: VADL Group Specification (multiple group definitions only for illustration, at most one group declaration is allowed)

| $\langle expr \rangle$      | $ ::= \langle literal \rangle   \langle rep \rangle   \langle alt \rangle   \langle perm \rangle   \langle seq \rangle \\   (' \langle expr \rangle ')' $ |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\langle literal \rangle$   | $::= \langle identifier \rangle$                                                                                                                          |

| $\langle rep \rangle$       | $::= \langle \textit{identifier} \rangle `<' \langle \textit{num} \rangle `' \langle \textit{num} \rangle `>'$                                            |

| $\langle alt \rangle$       | $::= \langle expr \rangle ` ` \langle alt \rangle   \langle expr \rangle$                                                                                 |

| $\langle seq \rangle$       | $::= \langle expr \rangle `.' \langle seq \rangle   \langle expr \rangle$                                                                                 |

| $\langle perm \rangle$      | $::= `{`{}, {perm-list}} `{}'$                                                                                                                            |

| $\langle perm-list \rangle$ | ::= $\langle expr \rangle$ ', ' $\langle perm-list \rangle \mid \langle expr \rangle$                                                                     |

Listing 4.2: The extended regular expression grammar specified in BNF

#### Constraints

Additionally, groups matched by the regular expression have to satisfy all specified constraints, which are annotations (in square brackets) written before the group definition. There are two types of constraints: *assertions* and *stop* constraints. Assertions have to be satisfied by all constraints and are checked once after a group was successfully matched by the regular expression.

Stop constraints are checked after every instruction consumed by the regular expression to determine if matching should be *stopped*. The group has to conform to the regular expression still, but this prevents any more instructions from being consumed. This can be used to specify distributed encodings.

Listing 4.3 shows an example of some common group constraints. This architecture uses a distributed encoding with a parallel bit, meaning groups should end with an instruction with the par bit set to zero. The first constraints also demonstrate the first use of the group name, which can be used like an array to extract concrete instructions at a specific index (the first constraint uses the parallel bit of the last instruction in the group) and to access the group's length (used in the second constraint).

#### 4. Implementation

Constraints can also contain quantified expressions, as shown in listing 4.3 and listing 4.4. The bound variables are restricted to some subset of instructions which corresponds to the union of the listed operations, so the variable in **forall a in** {A,LD} will be every instruction in the group that is part of either operation A or LD (or both). Notably, an instruction that has been matched via a specific operation in the regular expression can be matched via another operation (that it is also part of) in a constraint, as demonstrated in listing 4.3 where LD is a superset of LD\_LOAD. This existential (**exists**) and universal quantification (**forall**) have the same semantics as in first order logic. The only syntactical asymmetry between the two is that **exists in** {...} can be used as a shorthand for **exists** newVar in {...} then true.

```

instruction set architecture DSP = {

format F : Bits<32> =

2

{ par

[21]

3

, rs2

[20..16]

4

rs1

[15..11]

5

6

rd

[10..6]

7

opcode [5..0]

8

9

// ...

10

11

[ VLIW(VLIW.length - 1).par = 0 stop ]

12

[ VLIW.length <= 3 assert ]

13

[ forall a in {A, LD_LOAD}, b in {A, LD_LOAD} then a.rd != b.rd assert

14

group VLIW = A<0..2>.LD<0..1>.J<0..1>

16 }

```

Listing 4.3: Basic VADL Group Constraints

Notably, **forall** a **in** {A}, b **in** {B} **then** ... is not equivalent to **forall** a **in** {A} **forall** b **in** {B} **then** ... because for a specific **forall**, a specific instruction is never contained in multiple variables. To achieve the same behavior in the second case, a != b & ... has to be added to the condition.

The group indexing expressions and bound variables from quantifiers can be used in two ways: for accessing format fields (as shown in listing 4.3) and for checking membership of a specific operation (as shown at the end of listing 4.4, using the  $\in$  binary operator). These instruction values are, however, also fully integrated into VADL's type (inference) system. So a format field access is only valid if that instruction expression is guaranteed to contain it (i.e. the intersection of format fields in the instructions in the specified operations), consequently group indexing expressions can only be used to access format fields that are available on all instructions (because they are not restricted so some subset as in quantified expressions).

```

1 VLIW.length // number of instructions in the group

2 VLIW.bitLength // number of bits in the group

3

4 forall a in {A, LD_LOAD}, b in {A, LD_LOAD} then ...

5 exists i in {A, J} then ...

6 exists in {ALU}

7

8 VLIW(1) // the second instruction in the group

9 VLIW(VLIW.length - 1) // the last instruction in the group

10

11 VLIW(0) ∈ ALU_FP

12 i ∈ ALU_FP

```

Listing 4.4: VADL Group Constraint Expression Syntax.

#### **Group Counter**

Finally, when specifying a VLIW architecture, the program counter register needs to be declared using **group counter** as shown in listing 4.5.

(b) The repetition a < 2..4 >.

Figure 4.1: Examples for a DFA representation of the regular expression extensions.

#### 4.3 Decoding with Automatons

#### 4.3.1 Automatons and Extended Regular Expressions

We chose regular expressions because they are easy to understand and can be efficiently parsed. But there are still multiple ways to implement extended regular expressions.

The most commonly used approach uses deterministic finite automatons (DFAs), which can express standard regular expressions very well. In our extended version however, there is the problem that permutations and repetitions can generally not easily be expressed as a DFA. (We also did not want to use nondeterministic finite automatons *NFAs*, which are generally slower and require allocating memory at runtime.)

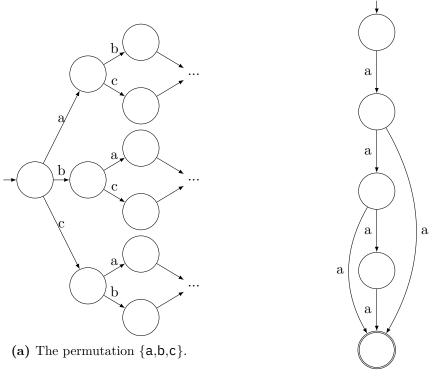

Figures 4.1a and 4.1b illustrate the blowup in the DFA that occurs in these cases. For a permutation of n elements, all possible n! orderings have to be covered by generating an automaton with  $2^n$  states. In the case of more complex elements (not just literals), these elements have to be duplicated as well. Theoretically, the same problem also applies to repetitions, though currently only literals can be repeated and not more complex subexpressions.

$$count_1 = 0$$

$$count_1 = 0$$

$$count_1 + +$$

if  $count_1 \ge 1$

$$count_2 = 0$$

$$consume A, if  $count_2 < 2$

$$count_2 + +$$

if  $count_2 \ge 1$$$

$\label{eq:Figure 4.2: A nondeterministic counter automaton matching the regular expression A < 1..2 >. A < 1..2 >.$

An alternative approach is to model these cases not with states, but with variables (called *counters*) which have no problem with enumerating these exponentially many states. Transitions between states then have *conditions* and *actions* (in addition to a symbol to consume) to read and update the counters. Somewhat counterintuitively however, a naive translation again results in a nondeterministic automaton, which is illustrated in figure 4.2 where state 1 has multiple possible next states if *count*<sub>1</sub> is 1. This occurs for example when parsing AAA, which could be parsed as A followed by AA or AA followed by A.

A standard regular expression can be converted into a NFA and then a DFA, e.g. using the powerset construction algorithm. But as described above, counters also introduce nondeterminism, which cannot be transformed away anymore by creating more states (without again resulting in automatons as in figure 4.1). This is because in a NFA with counters, each path might have different values for the counters. The powerset algorithm would model a NFA that might be in state X or Y as some DFA state XY, but with counters, there are multiple such states XY, each with different counter values.

Because we still wanted to implement a DFA with counters, we chose to only support a subset of extended regular expressions (which can be converted into a deterministic automaton). This subset consists of all standard regular expressions plus all extended regular expressions where consuming a token modifies at most one counter (i.e. avoiding counter non-determinism). Some valid and invalid examples:

- A.{A,B,C}: valid

- A<1..2>.B.A<1..2>: valid

- A<1..2>.A<1..2>: invalid (reason described above)

- {AB,AC,D}: invalid (permutation has common prefix)

#### 4.3.2 Generating Automatons

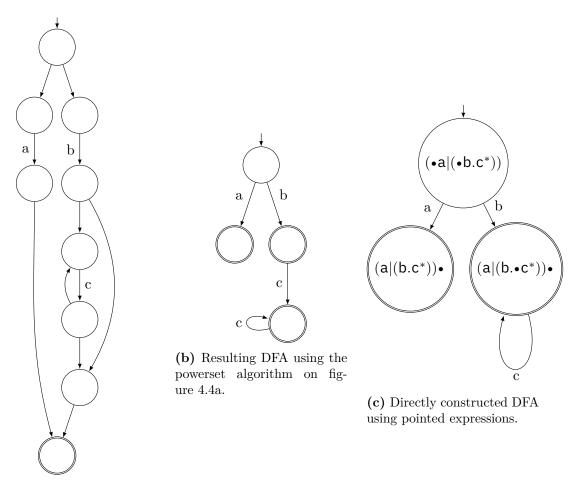

The algorithm for generating deterministic counter automatons (as described in the previous section) is not based on the commonly used Thompson's construction, but uses *pointed regular expressions* as introduced in [ACT10] (and this section reuses much of the formalism of that paper).

These points are inserted into a regular expression to track the intermediate states between the start and accepting states. When a token is consumed, it can be matched if and only if there exists a matching literal preceded by a point, and after that, the point moves over the token and further to the right. One way to think about this is that everything to the left of a point has already (successfully) been consumed, while everything to the right of the point still has to be consumed. Nondeterminism can be modeled by introducing multiple points, which correspond to multiple parts of the regular expression that might match the next token. This enables converting a regular expression directly into a DFA (instead of a NFA as with Thompson's construction).

Figure 4.3 demonstrates this with an example. The initial state is obtained by prefixing the regular expression with a point. In step 2, A can be matched because there exists a point followed by that token  $(\bullet A)$  in the current state, and the point moves over (so conceptually into  $A \bullet$ ). After that, an alternative creates two points, as indeed either B or C can be consumed now. As the next token is B, the point before C is removed and only the token before B is moved along towards the right. After consuming D, the end of the alternative expression is reached and the point moves out of and after the alternative itself. This is also an accepting state as nothing remains to be parsed to the right of the point. The non-accepting trap state of NFAs corresponds to the pointed expression with no remaining points.

The final implementation in VADL will, however, not match strings by moving points around, but by first constructing an automaton based on this concept. The pointed regular expression are the states in that automaton and the transitions depend on which literals are preceded by points (as shown in figure 4.4c). In that specific example, the pointed automaton is minimal, that is however not always the case (see [ACT10] for a detailed discussion).

- 0. Initial state •A.(B.D|C)

- 1. After consuming  $A = A.(\bullet B.D|\bullet C)$

- 2. After consuming  $B = A.(B.\bullet D|C)$

- 3. After consuming  $D = A.(B.D|C) \bullet$  (accepting state)

Figure 4.3: An example for using pointed regular expression to match an input string ABD against A.(B.D|C).

(a) NFA from Thompson's construction.

Figure 4.4: Comparing Thompson's construction with pointed expressions on the regular expression  $(a|(b.c^*))$ .

#### Formal Specification of Extended Pointed Expressions

More formally, our extended pointed expression language (in a slightly simplified notation, E + E being the alternative) conforms to the grammar

$E ::= a \mid \bullet a \mid E + E \mid E.E \mid \{E, \dots, E\} \mid \bullet \{E, \dots, E\} \mid E^{a..b} \mid \bullet E^{a..b}$

with  $a \in \Sigma$  (some alphabet, such as characters or instructions). This is called a *pointed item*, a pointed expression itself is a pair  $\langle e, b \rangle$  where e is a pointed item and b is a boolean signifying whether there is a point after the expression (so  $e \bullet$ ). Notably, points are never placed in front of alternatives or sequences but always moved inside, which is not the case for permutations and repetitions as these will not be handled via duplication of pointers, but using counters.

To add a point (e.g. for the initial state or in operations introduced later on) to the start of a pointed item, the *broadcast operator*  $\bullet(\cdot)$  is used. This operator is needed because points are only valid before literals, permutations and repetitions (i.e. not before alternatives and sequences). Intuitively, it moves the point inside the subexpression as necessary, e.g.  $\bullet(A^{0..1} + B) = \langle \bullet A^{0..1} + \bullet B, \text{true} \rangle$  representing  $(\bullet A^{0..1} + \bullet B) \bullet$ .

$$\begin{aligned} \bullet(\bullet e) &= \langle \bullet e, \text{false} \rangle \\ \bullet(a) &= \langle \bullet a, \text{false} \rangle \\ \bullet(a) &= \langle \bullet a, \text{false} \rangle \\ \bullet(e_1 + e_2) &= \bullet(e_1) \oplus \bullet(e_2) \\ \bullet(e_1.e_2) &= \bullet(e_1) \odot \langle e_2, \text{false} \rangle \\ \bullet(\{e_1, \dots, e_n\}) &= \begin{cases} \langle \bullet\{e_1, \dots, e_n\}, \text{true} \rangle & \text{if } \forall \langle e', b' \rangle \in \{\bullet(e_1), \dots, \bullet(e_n)\}.b' = \text{true} \\ \langle \bullet\{e_1, \dots, e_n\}, \text{false} \rangle & \text{else} \end{cases} \\ \bullet(e^{a..b}) &= \begin{cases} \langle \bullet e^{a..b}, \text{true} \rangle & \text{if } a = 0 \\ \langle \bullet e^{a..b}, \text{false} \rangle & \text{else} \end{cases} \end{aligned}$$

where  $\oplus$  and  $\odot$  are helper operators:

$$\begin{split} \langle e_1', b_1' \rangle \oplus \langle e_2', b_2' \rangle &= \langle e_1' + e_2', b_1' \vee b_2' \rangle \\ \langle e_1', b_1' \rangle \odot \langle e_2', b_2' \rangle &= \begin{cases} \langle e_1'. e_2', b_1' \rangle & \text{if } b_1' = \text{false} \\ \langle e_1'. e_2'', b_2' \vee b_2'' \rangle & \text{else, with } \bullet (e_2') = \langle e_2'', b_2'' \rangle \end{cases} \end{split}$$

For literals, permutations and repetitions, the point is added before the corresponding expression. Furthermore, permutations and repetitions can in some cases match zero length inputs (so a trailing point has to be added). For alternatives, the point is added to both subexpressions (and there is a point after the expression if at least one of the subexpressions ends with a point). For sequences, either the first subexpression is still being matched, or the first subexpression is finished and thus the point has to be moved into the second subexpression. The broadcast operator is then also extended to pointed expressions:

$$\bullet(\langle e, b \rangle) = \langle \bullet e', b \lor b' \rangle \text{ where } \bullet(e) = \langle e', b' \rangle$$

The central operation of pointed expressions is the *move* operation, which consumes the next input token and moves the points accordingly (as shown in figure 4.3).

This is also where conditions and actions are first introduced. They are specified via a counter identifier. There are two different action types:

- ACTBITSET $(c, idx: \cdot)$  which sets the *idx*-th bit of counter named c, and

- ACTINC(c) which increments the counter c by one.

The possible condition types are:

- CONDGREQ $(c, v: \cdot)$  to check if the counter value is greater or equal the given value,

- CONDLE $(c, v: \cdot)$  to check if the counter value is smaller than the given value,

- CONDBITCLEARED $(c, idx: \cdot)$  to check if the *idx*-th bit is set in the counter value,

- CONDRESTFULL(c, exc: es, width: w) to check if the counter has the lowest w bits set (except for the bits in the list es which can be unset still), and

- CONDRESTREMAINS(c, exc: es, width: w) to check if the counter has an unset bit (which is not in the list es) in the lowest w bits.

move(e, t, p) gives a list of transitions when reading a token t in state (i.e. pointed expression) e, each with a next state (pointed expression), conditions and actions. p is a string that is used to identify the current position in the expression to use as the counter identifier. Its value is arbitrary but has to be unique for every element of the expression.

First, for the unpointed case, literal expressions don't change (in equation (4.1)), and sequences and permutations use a version of the helper operators that also collect any conditions and actions from the recursive calls (in equations (4.2) and (4.3)).

For repetitions, there are two possibilities (in equation (4.4)): if there's no trailing point in the processed subexpression (b' is false) then nothing should happen as any potential points are still moving inside e', otherwise the current iteration of the repetition is finished and there are two possible next states (either another iteration is needed because the counter is below the minimum value and so the point is moved back to the start, or the whole repetition was successfully matched and the true in the tuple denotes a trailing point). Note how this can introduce nondeterminism as both of these conditions might be true.

For permutations (equation (4.5)), all possible combinations of the processed subexpressions have to be considered. If none of the subexpressions have a trailing point (|I'| = 0), then once again nothing should happen while the points move inside of the expression.