# Integrated Code Motion and Register Allocation

# DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

# Doktor der Technischen Wissenschaften

by

# Gergö Barany

Registration Number 0026139

| to the Faculty of Informatics<br>at the Vienna University of Techn | ology         |              |  |  |  |

|--------------------------------------------------------------------|---------------|--------------|--|--|--|

| Advisor: ao. Univ. Prof. DiplIng. Dr. Andreas Krall                |               |              |  |  |  |

| The dissertation has been review                                   | ed by:        |              |  |  |  |

|                                                                    | Andreas Krall | Alain Darte  |  |  |  |

| Vienna, 14 <sup>th</sup> January, 2015                             |               | Gergö Barany |  |  |  |

# Acknowledgements

Many people were very patient with me over the last few years. Thanks.

# Abstract

Code motion and register allocation are important but fundamentally conflicting program transformations in optimizing compiler back-ends. Global code motion aims to place instructions in less frequently executed basic blocks, while instruction scheduling within blocks or regions (all subsumed here under 'code motion') arranges instructions such that independent computations can be performed in parallel. These optimizations tend to increase the distances between the definitions and uses of values, leading to more overlaps of live ranges. In general, more overlaps lead to higher register pressure and insertion of more expensive register spill and reload instructions in the program. Eager code motion performed before register allocation can thus lead to an overall performance decrease.

On the other hand, register allocation before code motion will assign unrelated values to the same physical register, introducing false dependences between computations. These dependences block opportunities for code motion that may have been legal before assignment of registers. This is an instance of the phase ordering problem: Neither ordering of these phases of code generation provides optimal results. A common way to sidestep this problem is by solving both problems at once in an integrated fashion.

This thesis develops a fully integrated approach to global code motion and register allocation. The result is an algorithm that determines an arrangement of instructions that leads to minimal spill code while performing as much global code motion and scheduling for parallelism as possible. Based on an overlap analysis that determines all the possible interferences between live ranges when taking all possible arrangements of instructions into account, the algorithm constructs a register allocation problem such that the solution encodes code motion information to ensure a legal allocation. A candidate selection pass determines which live ranges should be considered for reuse of a processor register. The selection process includes a tuning parameter to study the trade-off between global code motion and spilling, and can be performed in a heuristic or an optimal way.

The results show that in general, global code motion should be careful to take register pressure into account. Except for rare cases where register use is low, compilers should focus on arranging code such that minimal spilling is required.

# Contents

| Al  | ostra                                                        | ct                                                                                                                                                                                                                                                                                                         | v                                              |

|-----|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Co  | nter                                                         | nts                                                                                                                                                                                                                                                                                                        | vii                                            |

| Lis | st of                                                        | Figures                                                                                                                                                                                                                                                                                                    | viii                                           |

| Lis | st of                                                        | Tables                                                                                                                                                                                                                                                                                                     | ix                                             |

| 1   | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8 | Compiler back-end program representations Static single assignment (SSA) form Register allocation and spilling Instruction scheduling Global code motion Phase ordering between code motion and spilling Motivation: A simple example Global code motion with spilling Limits of 'optimal' code generation | 1<br>1<br>2<br>3<br>4<br>4<br>4<br>6<br>7<br>9 |

| 2   | Rela<br>2.1<br>2.2<br>2.3<br>2.4                             | Instruction scheduling                                                                                                                                                                                                                                                                                     | 15<br>15<br>16<br>20<br>22                     |

| 3   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                              | Range Overlap Analysis Traditional overlap analysis                                                                                                                                                                                                                                                        | 25<br>25<br>26<br>34<br>37<br>38               |

| 4   | <b>Reu</b> 4.1                                               | The candidate selection problem                                                                                                                                                                                                                                                                            | <b>41</b>                                      |

|                                                      | 4.2                                             |                                                                                                                                                                                                    | 43                                              |

|------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

|                                                      | 4.3                                             | T · · · · · · · · · · · · · · · · · · ·                                                                                                                                                            | 44                                              |

|                                                      | 4.4                                             | Balanced reuse candidate selection                                                                                                                                                                 | 46                                              |

| 5                                                    | Spil                                            | 0                                                                                                                                                                                                  | <b>49</b>                                       |

|                                                      | 5.1                                             | • 0                                                                                                                                                                                                | 49                                              |

|                                                      | 5.2                                             | Spilling with reuse candidate information                                                                                                                                                          | 51                                              |

|                                                      | 5.3                                             |                                                                                                                                                                                                    | 53                                              |

|                                                      | 5.4                                             | Final instruction scheduling                                                                                                                                                                       | 54                                              |

| 6                                                    | Exp                                             |                                                                                                                                                                                                    | <b>55</b>                                       |

|                                                      | 6.1                                             | Implementation issues                                                                                                                                                                              | 55                                              |

|                                                      | 6.2                                             | Experimental methodology                                                                                                                                                                           | 58                                              |

|                                                      | 6.3                                             | Results                                                                                                                                                                                            | 59                                              |

|                                                      | 6.4                                             | Results of heuristic GCMS                                                                                                                                                                          | 71                                              |

| 7                                                    | Con                                             | aclusions                                                                                                                                                                                          | <b>75</b>                                       |

| Bi                                                   | bliog                                           | graphy                                                                                                                                                                                             | 77                                              |

|                                                      |                                                 |                                                                                                                                                                                                    |                                                 |

|                                                      |                                                 | List of Figure                                                                                                                                                                                     | $\mathbf{S}$                                    |

| 1.1                                                  | Ex                                              |                                                                                                                                                                                                    | <b>S</b>                                        |

| 1.1<br>1.2                                           |                                                 | List of Figure                                                                                                                                                                                     |                                                 |

|                                                      | $O_{I}$                                         | cample program with global dependence graph and control flow graph                                                                                                                                 | 6                                               |

| 1.2                                                  | O <sub>I</sub>                                  | cample program with global dependence graph and control flow graph otimization using GCM and GCMS for a three-register processor                                                                   | 6<br>8                                          |

| 1.2<br>1.3                                           | O <sub>I</sub><br>Co                            | cample program with global dependence graph and control flow graph obtimization using GCM and GCMS for a three-register processor onflict graphs for each of the program variants from Figure 1.2  | 6<br>8<br>9                                     |

| 1.2<br>1.3<br>1.4                                    | Op<br>Co<br>Co<br>No                            | cample program with global dependence graph and control flow graph obtimization using GCM and GCMS for a three-register processor onflict graphs for each of the program variants from Figure 1.2  | 6<br>8<br>9<br>11                               |

| 1.2<br>1.3<br>1.4<br>3.1                             | Or<br>Co<br>Co<br>No                            | cample program with global dependence graph and control flow graph obtimization using GCM and GCMS for a three-register processor onflict graphs for each of the program variants from Figure 1.2  | 6<br>8<br>9<br>11<br>26                         |

| 1.2<br>1.3<br>1.4<br>3.1<br>3.2                      | Op<br>Co<br>Co<br>No<br>Illu<br>Ex              | cample program with global dependence graph and control flow graph obtimization using GCM and GCMS for a three-register processor onflict graphs for each of the program variants from Figure 1.2  | 6<br>8<br>9<br>11<br>26<br>27                   |

| 1.2<br>1.3<br>1.4<br>3.1<br>3.2<br>3.3               | Or<br>Co<br>Co<br>No<br>Illu<br>Ex<br>Gr<br>So  | cample program with global dependence graph and control flow graph                                                                                                                                 | 6<br>8<br>9<br>11<br>26<br>27<br>29             |

| 1.2<br>1.3<br>1.4<br>3.1<br>3.2<br>3.3<br>3.4        | Or<br>Co<br>Co<br>No<br>Illu<br>Ex<br>Gr<br>So  | cample program with global dependence graph and control flow graph obtainization using GCM and GCMS for a three-register processor onflict graphs for each of the program variants from Figure 1.2 | 6<br>8<br>9<br>11<br>26<br>27<br>29<br>35       |

| 1.2<br>1.3<br>1.4<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Or<br>Co<br>No<br>Illi<br>Ex<br>Gr<br>So<br>Lin | cample program with global dependence graph and control flow graph                                                                                                                                 | 6<br>8<br>9<br>11<br>26<br>27<br>29<br>35<br>36 |

| 5.2 | Sample $\varepsilon$ edge cost matrix for modeling avoidable live range overlaps | 51 |

|-----|----------------------------------------------------------------------------------|----|

| 5.3 | Conflict graph for the example program from Figure 1.2, with dashed edges        |    |

|     | representing $\varepsilon$ edges in the PBQP graph                               | 52 |

| 5.4 | The code motion impact of allocating the example program for processors          |    |

|     | with various numbers of registers                                                | 53 |

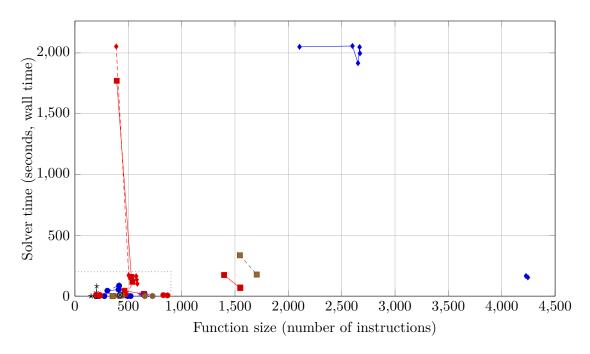

| 6.1 | Time taken by the ILP solver for problems of various sizes $(\beta = 0)$         | 67 |

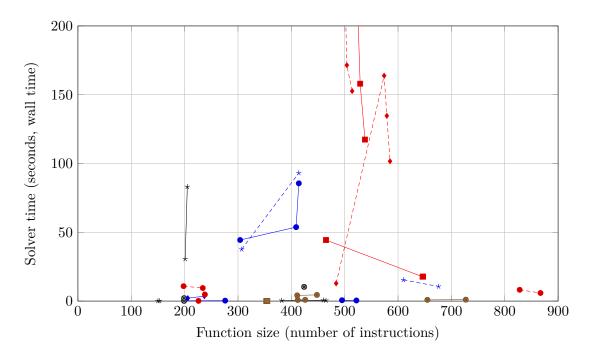

| 6.2 | Time taken by the ILP solver for problems of various sizes, detail of Figure 6.1 |    |

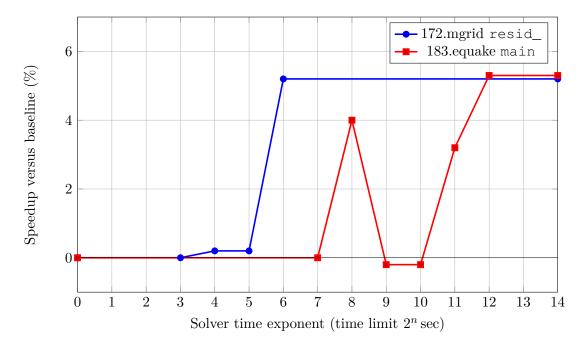

| 6.3 | Influence of solver time on the performance of selected benchmarks               | 68 |

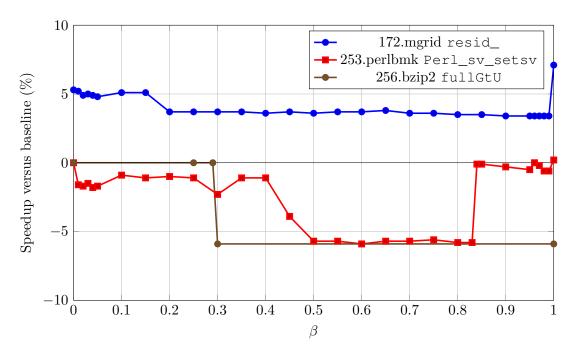

| 6.4 | Influence of the $\beta$ parameter on the performance of selected benchmarks     | 70 |

|     |                                                                                  |    |

|     |                                                                                  |    |

|     |                                                                                  |    |

|     |                                                                                  |    |

|     | List of Table                                                                    | S  |

| 3.1 | Blame terms computed for the example program, listing instruction placements and missing dependence arcs that may cause overlaps | 31 |

|-----|----------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1 | Execution times of benchmark programs with various GCMS configurations,                                                          |    |

|     | inlining threshold 225                                                                                                           | 61 |

| 6.2 | Execution times of benchmark programs with various GCMS configurations,                                                          |    |

|     | inlining threshold 450                                                                                                           | 63 |

| 6.3 | Static properties of selected benchmark functions with various GCMS config-                                                      |    |

|     | urations                                                                                                                         | 65 |

| 6.4 | Execution time speedups of benchmark programs compiled with various GCMS                                                         |    |

|     | configurations with heuristic candidate selection                                                                                | 72 |

| 6.5 | Execution time speedups of benchmark programs compiled with various GCMS                                                         |    |

|     | configurations with heuristic candidate selection and hoisting of uses disabled.                                                 | 73 |

CHAPTER 1

# Introduction

This thesis deals with the phase ordering problem between register allocation and global code motion. This chapter recalls the definitions of these problems, introduces a motivating example of the phase ordering problem, and gives a high-level description of the integrated solution developed as part of the thesis.

## 1.1 Compiler back-end program representations

The problems discussed in this thesis concern program transformations in compiler back-ends. The back-end is the compiler stage invoked after the input program has been parsed and statically analyzed, and high-level optimizations have been performed. The back-end maps some machine-independent representation of the computations in the program to the instruction set of some concrete target processor. The three main phases involved here are instruction selection, instruction scheduling/global code motion, and register allocation.

Instruction selection chooses the target instructions to implement the abstract computations in the program. In the rest of this thesis, we assume that this has been done, and the identities of instructions will remain unchanged. The scheduling/code motion and register allocation phases are discussed below.

In what follows, it is assumed that programs consist of one or more functions, but each function is processed by the compiler back-end in complete isolation from the other functions. From the point of view of the back-end, it therefore looks as if the function currently being compiled is identical to the input program. For simplicity, we will therefore sometimes use the phrase 'the (input) program' to mean 'the function in the input program currently being processed by the back-end'.

Instructions in the program are arranged in *basic blocks* (or simply *blocks*), which are single-entry single-exit regions in the program without transfers of control within the region. That is, a transfer of control in the program may only ever jump to some

block's beginning, and instructions that transfer control may only occur at the ends of blocks. Hence, unless a CPU exception is triggered, a block's first instruction is executed whenever all the other non-branching instructions in the block are executed before a branch is reached.

Within each block, instructions are arranged in some strict linear order. Processor architectures that allow instructions to be arranged in an explicitly parallel fashion (VLIWs) are not considered here.

A function's blocks are arranged in a *control flow graph* (CFG). In this graph, there is a directed edge from each basic block to each of the blocks that it may transfer control to. There is a special entry block where execution enters the function from its caller. The entry block has no predecessors in the CFG. It is assumed that every block in the function is reachable via CFG edges from the entry block. Every block is assumed to end in some instruction that jumps to another block in the same function or that returns to the function's caller.

An edge in the CFG is *critical* if it leads from a block with more than one successor to a block with more than one predecessor. A critical edge can be split by inserting a new, empty block on the edge. The rest of this thesis assumes a program representation in which all critical edges have been split, as this creates convenient targets for global code motion.

A central notion in what follows is that of dominance. A basic block a dominates a basic block b, written  $a \succeq_{\text{dom}} b$ , if every path in the CFG from the entry block to b must pass through a. Dominance is reflexive, transitive, and antisymmetric, and the entry block dominates every block. Each block's dominators are themselves ordered by dominance: If  $a \succeq_{\text{dom}} c$  and  $b \succeq_{\text{dom}} c$ , then  $a \succeq_{\text{dom}} b$  or  $b \succeq_{\text{dom}} a$ .

A block a strictly dominates b,  $a \succ_{\text{sdom}} b$ , if  $a \succeq_{\text{dom}} b$  and  $a \neq b$ . A block a immediately dominates b,  $a \succ_{\text{idom}} b$ , if  $a \succ_{\text{sdom}} b$  and for all other dominators d of b,  $d \succeq_{\text{dom}} a$ . Due to these properties, the basic blocks can be arranged in a dominator tree in which a is a parent of b if and only if  $a \succ_{\text{idom}} b$ . The entry block is necessarily at the root of the dominator tree.

Dominance can be generalized from basic blocks to instructions: For a given arrangement of instructions in the program, instruction i in block  $b_i$  dominates an instruction j in block  $b_j$  if  $b_i \succ_{\text{sdom}} b_j$  or  $b_i = b_j$  and i appears before j in that block. In Section 1.5, this will be generalized further to a notion of dominance on the program's global dependence graph.

# 1.2 Static single assignment (SSA) form

As an extension of Global Code Motion (Click 1995), our algorithm is based on a representation of the program in SSA (static single assignment) form (Cytron et al. 1991). In SSA, every value in the program has exactly one point of definition. Definitions from different program paths, such as updates of a value in a loop, are merged by inserting  $\phi$  pseudo-instructions. The  $\phi$  instructions are always placed at the beginnings of basic blocks and have one operand for each of the block's predecessors, representing the flow of

a value from that predecessor. The value defined by the  $\phi$  represents the merged value, i. e., the value that actually reaches that program point during execution of the program. The  $\phi$  instructions are removed from the final program by allocating their operands to identical physical registers or by introducing copy instructions (Sreedhar et al. 1999).

The particular form of SSA assumed in this thesis is strict SSA form. This is the commonly used variant of SSA that requires every instruction that defines a value to dominate all of the uses of that value. Where this condition is not already fulfilled by the input program, i.e., where some values may be undefined along some program paths, the program is assumed to have been transformed into a state where such cases are resolved explicitly by insertion of special undef pseudo-instructions and appropriate  $\phi$  instructions.

For the purposes of dominance in strict SSA form, the  $\phi$  instructions are treated as if each use of a merged value appeared at the end of the appropriate predecessor block. These uses are dominated by the definition even if, as is common in loops, the  $\phi$  itself appears before the definition of some value that it uses.

## 1.3 Register allocation and spilling

Register allocation is one of the classical optimizations in a compiler's back-end. It concerns the assignment of values (or *virtual registers*) used by a program to the processor's physical registers. Values that are not allocated to a register must be *spilled* (stored) to main memory and reloaded before use. As main memory accesses are significantly slower than register accesses, it is imperative for good performance to find an allocation that incurs the lowest possible number of executed spill and reload instructions. Spillers are typically guided by a model of *spill costs*: a static estimate of the numbers of executed loads and stores due to a spill.

A fundamental notion in register allocation is that of *liveness*: A value is live at a program point if it may be used at some later point without an intervening redefinition. A value's *live range* is the set of all program points where that value is live. Live ranges *conflict* or *overlap* if they intersect at some program point. The register allocator must ensure that at each program point, the set of all live values can be assigned to registers without conflict. If there are too many live values, some of them must be eliminated by spilling or other methods such as rematerialization, i. e., duplication of computations (Briggs, Cooper, and Torczon 1992).

The above definition of conflict can be refined further: Overlapping live ranges can be allocated to the same register if their values are provably equal. In particular, if an SSA value is defined by a copy instruction, it can be allocated to the same register as the source of the copy. This operation is known as *coalescing*. This thesis does not consider coalescing for two reasons. First, naïve coalescing can increase the number of live range conflicts, and it is not clear how to best integrate it with code motion. Second, many of the copies in target programs cannot, in fact, be coalesced because they are vital for establishing the correctness of SSA form in the presence of code motion and instructions that modify some of their input operands (see Section 3.4).

A value's live range depends crucially on the arrangement of instructions in the program. Since in the context of global code motion this arrangement is not fixed, traditional liveness analysis is not applicable to the work described in this thesis. Chapter 3 describes how overlaps between live ranges can be detected in the presence of global code motion.

The actual allocation of values to registers can be performed in one of several ways. While faster approaches exist (Poletto and Sarkar 1999), for the purposes of this work it is convenient to perform allocation on a *conflict graph*. The nodes of this graph are the live ranges in the program, and overlapping live ranges are connected by edges. Allocation is successful if a physical register can be assigned to each node such that no neighboring nodes are assigned the same register (or, more generally, overlapping registers). This approach is known as graph coloring (Chaitin 1982). The PBQP approach actually used in this work can be viewed as a generalization of graph coloring in which costs are assigned to allocations, and the overall cost is to be minimized (Scholz and Eckstein 2002; Hames and Scholz 2006).

## 1.4 Instruction scheduling

Instruction scheduling is the back-end phase that determines the ordering of instructions in each basic block. The schedule must respect *dependences*: Instructions may not appear before some condition is fulfilled. The most important case are data dependences between the uses of values and their definitions, i. e., values may not be used before they are defined. More general ordering dependences apply to instructions manipulating memory locations or CPU registers, where it must be ensured that values are not overwritten before the previous value is used for the last time. Dependences are usually captured in a *dependence graph*, an acyclic directed graph.

Any topological ordering of the dependence graph is in principle a legal schedule. However, not all schedules result in the same performance on modern processor architectures. On pipelined processors, instruction-level parallelism and thus performance can be improved by scheduling long computations early and at some distance from their uses, interleaving them with other computations. Scheduling can also take into account the number of different kinds of functional units in the processor and attempt not to schedule too many instructions that need the same functional unit at a time. Out-of-order execution, multiple instruction issue on superscalar processors, and register renaming performed by the CPU may to some extent alleviate bad scheduling decisions by the compiler, but scheduling can still be important in practice.

#### 1.5 Global code motion

The motion of instructions between basic blocks in this work is based on Global Code Motion (GCM) (Click 1995), a generalization of loop-invariant code motion techniques. It is *global* in considering an entire function at once. GCM is based on a representation of the program in SSA form and includes  $\phi$  instructions as normal nodes in the graph.

However, for the purposes of this work it is important that the dependence graph is acyclic to ensure schedulability. If we had dependence cycles, we would not be able to schedule instructions in a way that respects all dependences. In SSA form, cyclic data dependences can only occur as arcs from an instruction to a  $\phi$  earlier in a loop. We therefore only add those dependence arcs for  $\phi$  nodes that do not introduce such cycles. It is safe to ignore the cyclic dependences as long as we ensure that such instructions will not be sunk out of their loops.

In the graph, each instruction is associated with a list of basic blocks in which it may be placed legally. Some instructions are pinned to the blocks in which they appear originally:  $\phi$  instructions and branches model control flow and may never be moved to another block. We also forbid moving any instruction that may have a side effect (function calls and stores), any load except from the constant pool or stack, and any instruction that uses a physical register explicitly (copies to and from argument and return registers, instructions that use condition code registers). We use arcs to fix the order of those instructions within the block that may have side-effects on memory or access physical registers. This is overly conservative, but it saves us from having to solve NP-complete problems that come up when trying to schedule live ranges for pre-assigned physical registers (Darte and Quinson 2007). We do allow reordering of loads between instructions that may store. Instructions that are not pinned to their blocks may be moved to other blocks within the constraints given by dependence arcs.

Code motion is guided by the notion of dominance: A legally placed instruction dominates all of the instructions that depend on it and is dominated by all the instructions it depends on. The earliest and latest possible blocks for all instructions can be computed in two simple passes over the graph in topological order and reverse topological order. For each instruction, the earliest block necessarily dominates the latest block, and any intervening block on the path in the dominator tree from the earliest to the latest block is also deemed valid.

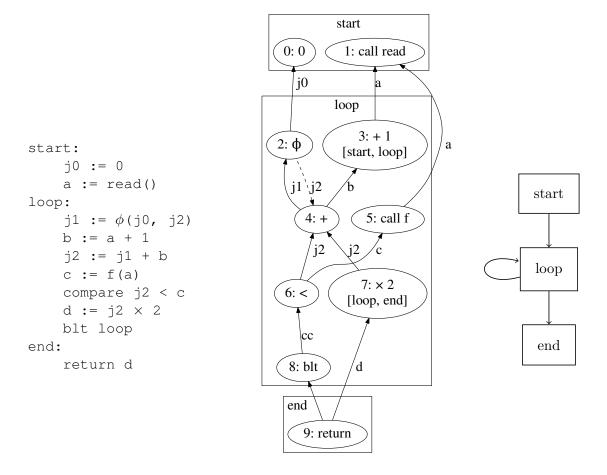

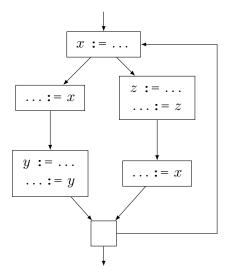

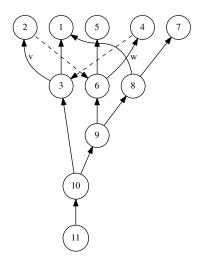

Figure 1.1 shows the code, the dependence graph, and the control flow graph for a program which will be used to illustrate concepts throughout this thesis. In the dependence graph, instructions are represented as nodes, and arcs in the dependence graph are labeled with the values that flow along them. Instructions are shown within basic blocks (rectangles), but some instructions may be moved to other blocks. These instructions are annotated with a list of the names of all the blocks in which they may be placed legally.

In the CFG in Figure 1.1, the start block dominates loop, which dominates end. The function calls, the  $\phi$ , the branch, and the return are not movable; all other instructions may in principle move as dependences allow. The branch depends on all arithmetic instructions except the multiplication, which is therefore the only arithmetic instruction legal for sinking out of the loop. The addition that computes b may be hoisted out of the loop because it only depends on values computed before the loop. The operations involving the j variables may not be hoisted due to the  $\phi$  and may not be sunk due to the dependence from the branch. The cyclic dependence due to the  $\phi$  is shown as a dashed arc, but is not present in the actual graph.

Figure 1.1: Example program with global dependence graph and control flow graph

The notion of dominance is lifted from fixed schedules of instructions to instructions in the dependence graph: An instruction i dominates an instruction j if there is a (possibly transitive) dependence from j to i, or if i's last legal block strictly dominates j's first legal block.

# 1.6 Phase ordering between code motion and spilling

Performing global code motion before spilling and register allocation (*prepass* scheduling) might lead to a program that requires many spills. Conversely, code motion and scheduling after register assignment (*postpass* scheduling) can be hindered by false dependences introduced by allocating unrelated values to the same physical register.

There are decomposed register allocators that separate spilling from allocation (Koes and Goldstein 2009), with the spiller inserting enough spill code to guarantee that there

is some valid allocation of the resulting program. It is possible to insert a code motion and scheduling pass after spilling but before allocation; however, care must be taken to ensure that the guarantee of a valid allocation is not invalidated by rearranging code.

Scheduling and code motion transformations may therefore attempt to balance their optimizations against the needs of register allocation, but they do not typically operate with an exact model of register usage. In previous work (see Chapter 2), many authors presented techniques to integrate local scheduling decisions within basic blocks with register allocation. In this work, we generalize such scheduling decisions to global code motion between blocks guided by the register allocator and based on its exact model of register demands.

The results of Govindarajan et al. (2003) suggest that, at least on modern out-of-order architectures, reducing the number of spills has more benefits than any other possible local scheduling decision. We expect this result to carry over to global code motion as well and provide experimental data that shows improvements due to our algorithm built on this premise. On embedded processors without out-of-order execution, more careful scheduling to make optimal use of the pipeline is more important. However, we believe that our transformation, which reduces the number of executed loads, is an optimization due to the removal of these expensive instructions. For this reason, our approach for integrated code motion and register allocation attempts to minimize overall spill costs while preserving as much freedom as possible for subsequent global code motion.

Our work attempts to strike a balance between the needs of register allocation and global code motion transformations. It makes use of the same graph structure to drive both spilling and code motion and can therefore handle these two important program transformations in a unified way. In our approach, spilling is performed not on a given schedule computed by a prepass scheduler, but rather a graph that represents all possible schedules. Some spills can be avoided by adding arcs to the graph to serialize computations. This can ensure that live ranges do not overlap, enabling the reuse of processor registers for unrelated values. The register allocator attempts to find a solution that incurs minimal spill costs but at the same time restricts the graph as little as possible. The resulting program contains a minimum of spill code but still has some freedom for aggressive code motion optimizations.

# 1.7 Motivation: A simple example

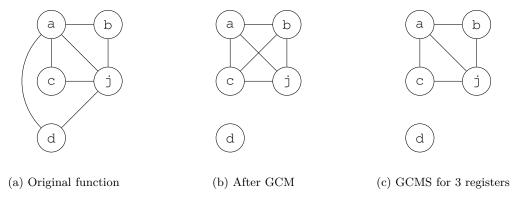

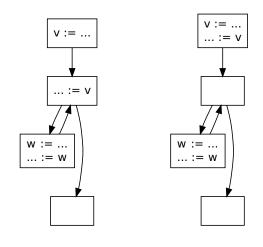

Figure 1.2 shows a few variants of the example program that was introduced above, adapted from the original paper on GCM (Click 1995). Figure 1.2a shows the same code as in Figure 1.1, repeated here for reference. It is easy to see that the computation of variable b is loop-invariant and can be hoisted out of the loop; further, the computation for d is not needed until after the loop. Since the value of its operand j2 is available at the end of the loop, we can sink this multiplication to the end block. Figure 1.2b illustrates both of these code motions, which are automatically performed by GCM. The resulting program contains less code in the loop, which means it can be expected to run faster than the original.

```

start:

start:

start:

j0 := 0

j0 := 0

j0 := 0

a := read()

a := read()

a := read()

b

:= a + 1

loop:

loop:

loop:

j1 := \phi(j0, j2)

j1 := \phi(j0, j2)

j1 := \phi(j0, j2)

b := a + 1

j2 := j1 + b

b := a + 1

j2 := j1 + b

c := f(a)

j2 := j1 + b

c := f(a)

compare j2 < c

c := f(a)

compare j2 < c

blt loop

compare j2 < c

d := j2 \times 2

blt loop

blt loop

end:

end:

end:

d := j2 \times 2

d := j2 \times 2

return d

return d

return d

(a) Original function

(b) After GCM

(c) GCMS for 3 registers

```

Figure 1.2: Optimization using GCM and GCMS for a three-register processor

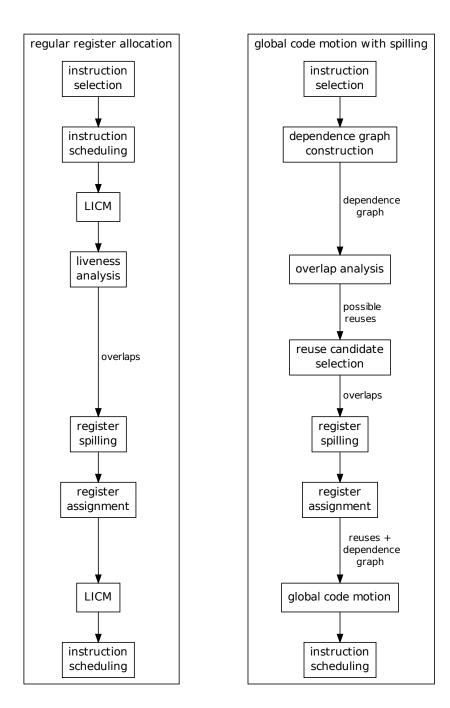

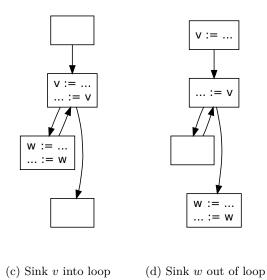

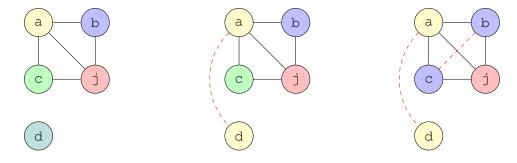

This expectation fails, however, if there are not enough registers available in the target processor. Consider the conflict graphs of the original program in Figure 1.3a and the program after GCM in Figure 1.3b. For simplicity, in the conflict graphs the  $\phi$ -related variables j0, j1, and j2 are merged into a single variable j. This merging is not possible in general and not needed for the GCMS algorithm, but it simplifies the presentation in this case.

Since after GCM the variable b is live through the loop, it conflicts with a, c, and j. Both a and c conflict with each other and with at least one of the j variables, so after GCM we need four CPU registers for a spill-free allocation. If the target only has three registers available for allocation of this program fragment, costly spill code must be inserted into the loop. As memory accesses are considerably more expensive than simple arithmetic, GCM would trade off a small gain through loop invariant code motion against a larger loss due to spilling.

Compare this to Figure 1.2c, which shows the result of applying our GCMS algorithm for a three-register CPU. To avoid the overlap of b with all the variables in the loop, GCMS leaves its definition inside the loop. This ensures that a register limit of 3 can be met. However, GCMS is not fully conservative: Sinking d out of the loop can be done without adversely affecting the register needs, so this code motion is performed by GCMS. Note that this particular code motion does lengthen j's live range, but the algorithm determines that this does not lead to unwanted live range overlaps in this case. The conflict graph for this variant of the program is shown in Figure 1.3c. Observe also that this result is specific to the limit of three registers: If four or more registers were

Figure 1.3: Conflict graphs for each of the program variants from Figure 1.2

available, GCMS would detect that unrestricted code motion is possible, and it would produce the same results as GCM in Figure 1.2b.

The idea of GCMS is thus to perform GCM in a way that is more sensitive to the needs of the spiller. As illustrated in the example, code motion is restricted by the choices of the register allocator, but only where this is necessary. In functions (or parts of functions) where there are enough registers available, GCMS performs unrestricted GCM. Where there is higher register need, GCMS serializes live ranges to avoid overlaps and spill fewer values.

In contrast to most other work in this area, GCMS does not attempt to estimate the register needs of the program before or during scheduling. Such models cannot predict which spilling and allocation decisions will be made by the register allocator. This means that such algorithms can be overly conservative. For example, the IPS algorithm (see Section 2.2.1) schedules basic blocks before register allocation based on a precomputed register limit. If the register allocator spills a value that is live across a basic block but not used in that block, this amounts to increasing the register limit for that block. However, as a purely prepass approach, IPS cannot take advantage of this change introduced by the spiller.

In contrast, GCMS computes a set of promising code motions that could reduce register needs if necessary. An appropriately encoded register allocation problem ensures that the spiller chooses which code motions are actually performed. Thus GCMS's code motion model is always fully synchronized with the actual spilling and allocation decisions make by the register allocator. Code motion and scheduling restrictions that are not needed to avoid spilling are not applied.

# 1.8 Global code motion with spilling

Given the dependence graph and legal blocks for each instruction, GCMS proceeds in the following steps: Overlap analysis determines for every pair of values whether their live ranges might overlap. The goal of this analysis is similar to traditional liveness analysis for register allocation, but with the crucial difference that in GCMS, instructions may move. Our overlap analysis must therefore take every legal placement and every legal ordering of instructions within blocks into account.

For every pair, the analysis determines whether the ranges definitely overlap in all schedules, never overlap in any schedule, or whether they might overlap for some arrangements of instructions. In the latter case, GCMS computes a set of code placement restrictions and extra arcs that can be added to the global dependence graph. Such restrictions ensure that the live ranges do not overlap in any schedule of the new graph, i. e., they enable *reuse* of the same processor register for both values.

Candidate selection chooses a subset of the avoidable overlaps identified in the previous phase. Not all avoidable overlaps identified by the analysis are avoidable at the same time: If avoiding overlaps for two register pairs leads to conflicting code motion restrictions, such as moving an instruction to two different blocks, or adding arcs that would cause a cycle in the dependence graph, at least one of the pairs cannot be chosen for reuse. GCMS must therefore choose a promising set of candidates among all avoidable overlaps. Only these candidate pairs will be considered for actual overlap avoidance by code motion and instruction scheduling. Since our goal is to avoid expensive spilling as far as possible, we try to find a candidate set that maximizes the sum of the spill costs of every pair of values selected for reuse.

Spilling and code motion use the results of the candidate selection phase by building a register allocation problem in which the live ranges of reuse candidates are treated as non-conflicting. The solution computed by the register allocator is then used to guide code motion: For any selected candidate whose live ranges were allocated to the same CPU register, we apply its code motion restrictions to the dependence graph. The result of this phase is a restricted graph on which we can perform standard GCM, with the guarantee that code motion will not introduce excessive overlaps between live ranges.

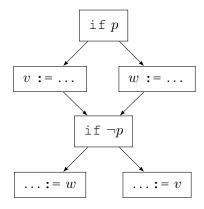

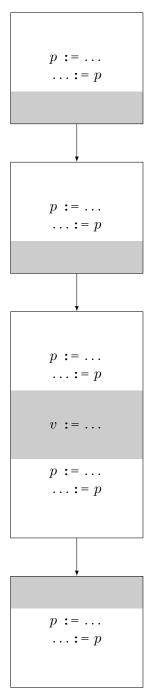

Figure 1.4 shows an abstract comparison of compiler back-end phases for regular register allocation and GCMS. In a typical case (as implemented in the LLVM compiler framework, for instance), instruction scheduling and loop-invariant code motion (LICM) are performed before the liveness analysis that feeds the spiller and register allocator. In our case, code motion and scheduling before spilling are not necessary; we only place instructions after spilling. Instead we build a dependence graph which is used both for code motion and for overlap analysis. Liveness analysis is replaced by two phases: overlap analysis to determine all the possibly overlapping live ranges, and selection of the set of pairs of possibly overlapping live ranges that will be presented to the register allocation phases. Spilling and register allocation proceed identically in GCMS and regular register allocation. Finally, GCMS uses the allocator's results to perform restricted global code

Figure 1.4: Comparison of phases in a compiler back-end using regular register allocation (left) and a back-end using integrated code motion and register allocation with GCMS (right)

motion and scheduling to determine the final arrangement of instructions in each block. A regular back-end can also follow register allocation with another round of LICM and scheduling to exploit remaining possibilities for optimization.

Each of the three main phases of GCMS is the topic of one of the following chapters.

## 1.9 Limits of 'optimal' code generation

The GCMS algorithm presented in this thesis formulates a specific model of integrated code generation and solves this model optimally. However, there can be cases where the generated code is not actually as fast as some other, equivalent code generated in some other way. This is due to several reasons.

First, not all data that would be needed for the generation of optimal code is available. In part, this is unavoidable due to the complexity of modern computer architectures: The execution time of a piece of code is not fixed but depends on the states of the processor pipeline and on the caches. For simple platforms, safe approximations of the hardware's worst-case behavior exist and can be exploited in code generation (Falk 2009; Lokuciejewski et al. 2010), but the exact behavior of an out-of-order processor is typically undocumented and essentially unpredictable at compile time.

Other performance-relevant data concerns the program itself. In particular, detailed basic block profiling information would allow a much more precise formulation of spill costs and the benefits of global code motion operations. However, the LLVM compiler framework does not provide this data at the required granularity: Basic block profiling data is available on the LLVM intermediate code level, but the lowering to target-specific code introduces new blocks and complex new control flow that makes it impossible in general to propagate profiling information to all points in the program. The cost model used by GCMS therefore relies on static estimates of block frequencies, which may not agree with actual dynamic frequencies.

Second, the cost model used by GCMS does not capture all aspects of spilling and code motion directly. While global code motion is guided by a cost model, the impact of artificial instruction ordering constraints on local schedule lengths is not modeled. This is based on the expectation that out-of-order execution will hide most of the associated costs (Govindarajan et al. 2003), but that is not always the case in practice. The spill cost model for candidate selection itself does not perform or predict the concrete spilling choices made by the decoupled spiller; it only minimizes the total sum of spill weights of overlapping live ranges. This is a simple and useful model, but there is no guarantee that it will always lead to the set of reuse candidates and associated schedules that absolutely minimize spilling.

Finally, some parts of GCMS rely on pre-existing, heuristic building blocks for simplicity. In particular, spilling is performed using the heuristic PBQP register allocator, and register assignment is not performed to avoid having to deal with out-of-SSA transformation. As the results in Chapter 6 show, both of these choices can sometimes cause paradoxical behavior in practice. Using an optimal formulation of spilling and register assignment with GCMS may be possible in theory. This would, however, lead to

much longer solver times. Additionally, the spilling problem itself is not fully solved yet: Even the careful optimal formulation of spilling in SSA form by Colombet, Brandner, and Darte (2011) leaves open the problem of optimal coalescing of the operands and results of  $\phi$  instructions.

# Related Work

This chapter summarizes the most relevant existing research into instruction scheduling and its relation to register allocation. General overviews of both topics are standard material in compiler textbooks (Aho, Lam, et al. 2006; Cooper and Torczon 2004; Muchnick 1997). These textbooks traditionally present scheduling and register allocation as separate topics without considering integrated approaches.

## 2.1 Instruction scheduling

In the absence of instruction pipelining, the ordering of instructions within basic blocks does not matter as long as all dependences are satisfied and the register use is not so large that it would cause spilling. Very early work in code generation thus focused on minimizing the number of instructions emitted and the number of registers needed. Under the unrealistic assumption of only evaluating expression trees, not DAGs, the simple Sethi-Ullman numbering algorithm produces code that is minimal in both register use and total number of instructions (Sethi and Ullman 1970). Solving the same problem for DAGs is NP-complete, but the Sethi-Ullman algorithm can be generalized to a heuristic for DAGs (Aho, S. C. Johnson, and Ullman 1977).

With the advent of pipelined architectures, scheduling became more important in order to exploit instruction-level parallelism<sup>1</sup>. Rymarczyk (1982) gives an early tutorial on programming for pipelined systems.

Finding a minimal-length schedule for a pipelined processor is NP-complete in general and is typically solved using heuristic list scheduling (Hennessy and Gross 1982; Gibbons and Muchnick 1986). List scheduling is an iterative algorithm that traverses a basic block DAG and emits instructions one by one, respecting dependences and various other

<sup>&</sup>lt;sup>1</sup>Instruction-level parallelism is often abbreviated ILP. In this thesis, the acronym ILP is used for *integer linear programming*, and instruction-level parallelism is spelled out in full or abbreviated as 'parallelism' when needed.

constraints. At each point, there are typically several instructions that are ready to be scheduled. The next instruction is selected heuristically based on considerations of latency, the length of the path to the end of the block, or availability of processor resources. In processors without pipeline interlocks, no instruction may be ready at a given time because all unscheduled instructions must wait for some data or resource to become available. In such cases, the scheduler must emit a no-op instruction. The criteria for selecting the next instruction to be scheduled may be captured formally in a rank function that assigns an integer-valued rank to each instruction in the DAG (Palem and Simons 1990). Ranks are usually precomputed immediately prior to scheduling. The list scheduler always selects an instruction of maximal rank among the ready instructions to be scheduled next, possibly using additional properties to break ties. For processors with complex pipelines, it can make sense to adapt the rank function on-the-fly depending on the amount of parallelism present in the code (Ertl and Krall 1992).

Besides heuristic list scheduling, there is also a body of work on optimal approaches. These can be based on formulations such as constraint logic programming (Ertl and Krall 1991), integer programming (Wilken, Liu, and Heffernan 2000), or enumeration with pruning (Shobaki and Wilken 2004). As with list scheduling, the goal of such models is usually to optimize for minimal total schedule length only.

# 2.2 Integrated scheduling and register allocation

Arranging instructions for minimal schedule length on a pipelined processor tends to lengthen live ranges and thus increase the number of live range overlaps. For example, the typical examples for list scheduling in the classic papers are based on hiding the latencies of load instructions by scheduling loads next to each other. However, this means that the loaded values take up registers earlier than they might be needed. Integrated approaches to scheduling and register allocation try to ensure that this kind of operation to exploit parallelism is only performed as long as it does not lead to excessive spilling.

The following sections mostly describe notable heuristic approaches to the problem. A recent survey article (Castañeda Lozano and Schulte 2014) discusses integrated combinatorial approaches.

#### 2.2.1 Integrated prepass scheduling

Integrated prepass scheduling (IPS) was the first attempt to perform scheduling while considering register use (Goodman and Hsu 1988). IPS is a modified list scheduler that integrates a standard latency-oriented list scheduler with another scheduler based on the Sethi-Ullman algorithm that aims at minimizing register usage. IPS runs before register allocation.

IPS keeps track of the number of available registers at each program point; this value is initialized before scheduling each block based on the results of a global liveness analysis. For each value that is used within the block, the number of uses is also computed. IPS assumes a basic block in single-assignment form. Instructions are initially scheduled as in

regular list scheduling. Each value's use count is decreased for each scheduled instruction that uses it. The number of available registers is decreased for each value defined by the last scheduled instruction, and increased for each value for which the last scheduled instruction was the last use.

Whenever the number of available registers is below a threshold (such as 1), IPS chooses the next instruction based on the second selection function. If possible, it chooses an instruction that frees a maximal number of registers. If no such instruction is available, IPS prefers an instruction that continues evaluating an expression that has been partially evaluated already. Otherwise, it chooses arbitrarily. IPS can thus sometimes exceed the given register limit, which may cause spilling later on.

IPS is run before a final register allocator which may insert spill code where IPS did not succeed in finding a schedule that keeps within the available register limit. Simulations show that IPS outperforms both prepass and postpass scheduling in terms of the number of processor cycles executed in the final program.

#### 2.2.2 DAG-driven register allocation

DAG-driven register allocation was introduced together with IPS (Goodman and Hsu 1988). It approaches the problem from the other direction first: Rather than scheduling the DAG while keeping register allocation in mind, DAG-driven register allocation performs allocation first and tries to minimize the false dependences introduced in the process.

DAG-driven register allocation is based on measuring the width of the DAG, which is the number of registers that would be needed if all parallelism were exploited by scheduling, and the height of the DAG, which is the length of the longest path. While the width of the DAG exceeds the number of available registers, false dependences are introduced to reduce parallelism. Each such operation may increase the DAG's height by making the critical path longer.

The allocator visits nodes in the DAG in topological order and assigns registers. For each instruction it prefers reusing a register that was used by one of its predecessors in the DAG since this does not add an extra dependence. If dependences must be added, the choice is guided by instructions' earliest issue times and earliest finish times, computed from the DAG. The allocator tries to limit the growth in the DAG's height by ensuring that the instructions with the highest earliest finish times reuse registers from instructions with the lowest earliest issue times.

Simulation results show that DAG-driven register allocation performs similarly to IPS, possibly slightly worse on highly pipelined machines and slightly better on others. The differences disappear with larger numbers of CPU registers.

The idea of DAG-driven register allocation was later generalized to global register allocation (Ambrosch et al. 1994). In dependence-conscious coloring, a graph-coloring global register allocator is informed by a collection of DAGs for the program's basic blocks. Whenever a live range is to be assigned to a CPU register, the allocator computes the impact of each possible assignment on the schedules. The allocator chooses a register that minimizes the increase in schedule lengths due to false dependences. Preliminary results

for this approach showed that it appeared effective at exploiting scheduling freedom if register pressure was not excessive.

#### 2.2.3 RASE

The RASE (Register Allocation with Schedule Estimates) algorithm (Bradlee, Eggers, and Henry 1991) decomposes register allocation into local and global allocation for live ranges that are only live within one block or across block boundaries, respectively. Global live ranges are allocated by a standard register allocator based on graph coloring. Local live ranges are allocated during a basic block scheduling pass that must meet a given register limit.

The register limits for basic blocks are computed by the global allocator as well, based on scheduling information computed beforehand. Based on two trial scheduling passes, one without a register limit and one with a very low register limit, RASE estimates a function that quantifies how each block's schedule length would increase for any possible register limit. Nodes representing these changes in costs, weighted by estimated block frequencies, are added to the global register allocation problem. The register limit for each block is the number of nodes representing that block in the allocation problem that have been assigned a color.

The final scheduler within each block is similar to IPS except that it may never exceed its register limit; spill code is inserted by the scheduler if necessary. Overall, RASE is found to generate code that is very similar to IPS, with a possible slight advantage on very large basic blocks.

#### 2.2.4 Parallel interference graph algorithm

Pinter (Pinter 1993) describes an algorithm based on the coloring of a parallel interference graph. This coloring gives a register allocation that does not introduce false dependences, so a simple postpass scheduling pass can exploit maximal parallelism. The basic algorithm considers one block at a time.

The parallel interference graph is constructed as follows. A node is created for each instruction, and any two instructions connected by a path in the dependence graph are connected by an edge. This graph is further enhanced with an edge between any two instructions that may not execute at the same time on a superscalar machine due to resource conflicts. For example, if there is only a single floating-point unit, all floating-point computations are connected by edges. The resulting graph captures all the pairs of instructions that may not execute in parallel. Its complement is then the graph connecting all pairs of instructions which may be scheduled in parallel; no false dependences should be introduced between these pairs. The union of this parallelism graph (in which instructions are represented by the live ranges they define) with the live range interference graph is the parallel interference graph that is to be colored. By construction, if a valid coloring exists, it does not introduce false dependences between instructions that may execute in parallel.

If no coloring can be found, some live ranges are spilled. Pinter does not present an experimental evaluation of this algorithm.

The parallel interference graph shares interesting similarities with the conflict graph that GCMS uses for integrated register allocation and code motion (see Section 5.2). However, the trade-offs are completely opposite: GCMS attempts to avoid spilling even if that means introducing false dependences, while Pinter's algorithm would rather spill than accept a false dependence, even if it might not disturb the schedule much.

#### 2.2.5 Norris and Pollock's algorithm

The BMW algorithm of Norris and Pollock (Norris and Pollock 1993) is also similar to the local scheduling part of GCMS. It starts out with constructing a global register interference graph that captures all the possible live range overlaps if all possible schedules are considered. The number of interferences is then reduced by removing those that correspond to the 'least likely' scheduling decisions. The appropriate arcs are added to the dependence graph to ensure that these scheduling decisions cannot be taken. These arcs that are not likely to change the final schedule are determined by examining the scheduler's rank function on the DAG: Nodes are considered unlikely to be scheduled after nodes of lower rank. During register allocation, additional arcs are added if necessary to further reduce the need for registers.

Several variants of the basic algorithm are evaluated on a simulator. The results show that the best variant always outperforms IPS. The reasons for this are not discussed, but it appears that this algorithm might lead to less spilling than IPS.

#### 2.2.6 URSA

The URSA (unified resource allocation) algorithm (Berson, Gupta, and Soffa 1993; Berson, Gupta, and Soffa 1999) treats registers and functional units in VLIW processors in a unified way and computes schedules with the intention of reducing excess resource requirements. The demand for resources (registers or functional units) is computed on a dependence DAG by decomposing it into allocation chains, which are sequences of instructions that can reuse some resource. Where the demand is too high, it is reduced by inserting dependence arcs or by spilling.

Crucially, the spilling performed by URSA and ILS, a variant of IPS developed for purposes of comparison with URSA (Berson, Gupta, and Soffa 1999), spills only parts of live ranges. (The authors refer to this as live range splitting.) This is compared to a variant of IPS that uses the simpler 'spill everywhere' approach in which entire live ranges are spilled to memory and reloaded before each use. The comparison of IPS, ILS, and URSA shows that both URSA and ILS vastly outperform IPS in simulations, especially for small numbers of registers. However, the improvement of URSA over ILS is much more modest. Thus it seems that a large part of the improvement due to URSA is not due to its complex resource allocation technique but rather due to sophisticated spilling.

#### 2.2.7 Register saturation

The URSA approach was studied further from the point of view of register saturation (Touati 2001), which is the maximal register need over all schedules of a given DAG. The register saturation can be computed exactly by finding the maximal antichain of a special dependence graph associated with a killing function that maps each live range to one instruction which is its last use. However, finding a maximizing killing function is NP-complete.

The study of register saturation uncovered cases where URSA's approach to computing the register demand from the dependence graph appears to underestimate the actual needs over all schedules. Heuristics for computing and reducing the register saturation by adding dependences are given and found near optimal through comparison with optimal solutions obtained by integer linear programming. However, the relationship to global register allocation is not studied. Later work in register saturation improves the heuristics by serializing not just individual live ranges, but entire sets of live ranges at a time (Xu and Tessier 2007).

#### 2.2.8 CRISP

The CRISP (combined register allocation and instruction scheduling) algorithm (Motwani et al. 1995) makes an interesting generalization to the integrated approaches discussed above. While older approaches tended to try to balance instruction-level parallelism against spilling and accept some spills, over time newer algorithms aimed more and more at eliminating spilling as far as possible (Govindarajan et al. 2003). In CRISP, this trade-off is captured in two model parameters that can be varied to study the problem space.

The heuristic CRISP scheduler is based on a standard list scheduler with a rank function. Using a standard rank function  $\gamma_S$  and a special register rank function  $\gamma_R$  that is meant to capture live range lengths, scheduling is performed with the new combined rank function  $\gamma = \alpha \gamma_S + \beta \gamma_R$  with the parameters  $\alpha, \beta \in [0, 1]$  and  $\alpha + \beta = 1$ . Simple experiments on random DAGs show that setting  $\beta = 1$  (i. e., focusing on reducing live range lengths) is effective in reducing the number of spills versus aggressive list scheduling.

In the context of this thesis, this work is mostly notable because GCMS uses a broadly similar model to balance global code motion and spilling (see Section 4.4.2).

# 2.3 Integrated code motion and register allocation

All of the work mentioned above considers only local instruction scheduling within basic blocks, but no global code motion. At an intermediate level between local and global approaches, software pipelining (Lam 1988) schedules small loop kernels for optimal execution on explicitly parallel processors. Here, too, careful integration of register allocation has proved important over time (Codina, Sánchez, and González 2001; Eriksson and Kessler 2012).

The following sections discuss the more notable (partly) global integrated allocators in more detail.

#### 2.3.1 RASER

RASER (Norris and Pollock 1995b) performs register allocation sensitive region scheduling. It is based on a region scheduling algorithm which uses a program dependence graph of hierarchically nested program regions. The algorithm estimates the amount of parallelizable computations in each node and tries to move code from regions with too many parallel computations to regions where the parallelism is not as high as the machine can accommodate.

RASER extends this by also computing the register demands of regions after applying IPS to schedule them. In regions with excess register pressure, RASER attempts to reduce the number of live values by duplication of computations. If possible and profitable (because it would not increase register pressure), the definition of each value used in such a region is duplicated before each use. The number of live values is updated on the fly.

After reducing register pressure below the limit wherever possible, RASER still allows normal code motion between regions, but only if they will not raise the register pressure above the register limit. Like many other approaches, RASER gives impressive improvements on machines with artificially few registers; later results on a machine with 16 registers are much more limited and more similar to ours, up to 3% at most (Norris and Pollock 1995a).

### 2.3.2 VSDG algorithm

N. Johnson and Mycroft (2003) describe an elegant combined global code motion and register allocation method based on the Value State Dependence Graph (VSDG). The VSDG is similar to the acyclic global dependence graph used by GCMS, but it represents control flow by using special nodes for conditionals and reducible loops (their approach does not handle irreducible loops) rather than our lists of legal blocks for each instruction. The graph is traversed bottom-up in a greedy manner, measuring 'liveness width', the number of registers needed at each level. Excessive register pressure is reduced by adding dependence arcs, by spilling values, or by duplicating computations. Unfortunately, we are not aware of any data on the performance of this allocator, nor the quality of the generated code.

The concept of liveness width is similar to Touati's 'register saturation', which is only formulated for basic blocks and pipelined loops. It is natural to try to adapt this concept to general control flow graphs, but this is difficult to do if instructions may move between blocks and into and out of loops. It appears that to compute saturation, we would need to build a detailed model of where each value may be live, and this might quickly lead to combinatorial explosion. GCMS is simpler because it tries to minimize overlaps without having to take a concrete number of available registers into account.

#### 2.3.3 Machine learning

Lokuciejewski et al. (2010) use machine learning to derive heuristics for loop-invariant code motion. Based on 73 different features such as instruction type, number of values live into, live out of, defined, and used in basic blocks, and loop nesting level, various models for moving code are trained on a benchmark set. The quantity to be optimized is the programs' worst-case execution time (WCET), which is estimated using standard tools. The authors find that their best model can sometimes substantially reduce WCET when compared to naïve loop-invariant code motion, with an average improvement of  $4.6\,\%$  on a processor with 16 general-purpose registers.

Unfortunately, the authors do not give any indication which program features appear most relevant for deciding whether to move any particular loop-invariant computations.

#### 2.3.4 Partly global approaches

Many authors have worked on what they usually refer to as global instruction scheduling problems, but their solutions are almost invariably confined to acyclic program regions, i. e., they do not perform loop invariant code motion (Bernstein and Rodeh 1991; Zhou, Jennings, and Conte 2003). The notable exception is work by Winkel (Winkel 2007) on 'real' global scheduling including moving code into and out of loops, as our algorithm does. Crucially, Winkel's optimal scheduler runs in two phases, the second of which has the explicit goal of limiting code motion to avoid lengthening live ranges too much. Besides considerable improvements in schedule length, Winkel reports reducing spills by 75 % relative to a heuristic global scheduler. In contrast to our work, Winkel compiled for the explicitly parallel Itanium processor, so his reported speedups of 10 % cannot be meaningfully compared to our results on our out-of-order target architecture (ARM Cortex-A9).

#### 2.4 GCMS

The GCMS algorithm presented in this thesis evolved in several steps. The initial phase was register reuse scheduling (Barany 2011). This algorithm was already based on the idea of computing all possible schedules and their impact on live range overlaps, and letting the PBQP register allocator's results determine how to modify the dependence graph to ensure that the final schedule is valid for the chosen allocation. Register reuse scheduling was a purely local approach. Candidate selection was performed using the greedy heuristics also used by GCMS. Simulator results showed that this algorithm was successful at reducing spills versus LLVM's baseline heuristics, which also try to schedule for minimal register pressure.

GCMS (Barany and Krall 2013) then arose as the generalization of register reuse scheduling to global code motion. Based on the same principles as register reuse scheduling, the overlap analysis was lifted to the global dependence graph. GCMS allows both optimal and heuristics candidate selection and fully global code motion along paths in the dominance tree. The results for GCMS showed very slight speedups over LLVM. In

retrospect, this was at least in part due to inaccuracies in the overlap analyses implemented at the time. Additionally, the optimal solver was ony applied to relatively small functions (up to 1000 instructions) and with a low time limit (60 seconds per instance). This thesis reports better results because these shortcomings have been resolved.

# Live Range Overlap Analysis

This chapter discusses one of the two major challenges in integrating global code motion with register allocation: the problem of analyzing which live ranges might overlap in the program if the final arrangement of instructions is not known. After a discussion of traditional overlap analysis on a fixed program, a novel way of analyzing overlaps in the presence of code motion is presented.

# 3.1 Traditional overlap analysis

The live ranges of two values v and w overlap at a program point if they are both live at that point. Compilers traditionally compute the sets of all program points where each value is live; these sets are variously called *live ranges* or *live intervals*.

Since values are live at all points where their current value might be used in the future, live ranges can be computed using a simple data flow analysis that proceeds backwards (i. e., against the direction of control flow). In this analysis values become live at each use, and liveness is propagated up towards the point of definition, computing fixed points for loops (F. Nielson, H. R. Nielson, and Hankin 1999). The analysis is applicable to all programs; faster liveness analysis algorithms are also available specifically for programs in SSA form (Boissinot et al. 2011).

Live ranges overlap if and only if their intersection is non-empty. For a function containing n values, an interference-graph based register allocation algorithm such as PBQP must check  $O(n^2)$  pairs of live ranges for overlap. These checks should therefore be very fast in practice. Common representations for live ranges include bit vectors with one bit per program point where the value is live, or sets of intervals of such program points. Alternatively, the liveness analysis only retains information on which basic blocks each value is live out of. An interference graph can then be reconstructed in an additional backward pass over each block (Cooper and Torczon 2004, section 13.5).

Figure 3.1: Nontrivial live range overlap in a non-SSA program.

# 3.2 Overlap analysis in the presence of code motion

The traditional methods described above all work on program representations in which the arrangement of instructions is fixed. They are therefore not directly suitable for integrating register allocation and code motion: The information computed by traditional liveness analysis would be invalidated by changes to the ordering or placement of instructions.

We must therefore develop an alternative formulation for the analysis of overlaps between live ranges in SSA form that does not refer to explicit live-out sets or sets of live program points.

#### 3.2.1 Characterization of overlaps in SSA form